Limitations, Configuration, Document revision history – Altera Embedded Peripherals IP User Manual

Page 133: Limitations -3, Configuration -3, Document revision history -3

provided to remove false timing paths. The frequency of the SPI master’s clock must be equal to or lower

than the frequency of the core’s clock.

Limitations

Daisy-chain configuration, where the output line

miso

of an instance of the core is connected to the input

line

mosi

of another instance, is not supported.

Configuration

The parameter Number of synchronizer stages: Depth allows you to specify the length of

synchronization register chains. These register chains are used when a metastable event is likely to occur

and the length specified determines the meantime before failure. The register chain length, however,

affects the latency of the core.

For more information on metastability in Altera devices, refer to

For more information on metastability analysis and synchronization register chains, refer to the

Quartus II Handbook.

Document Revision History

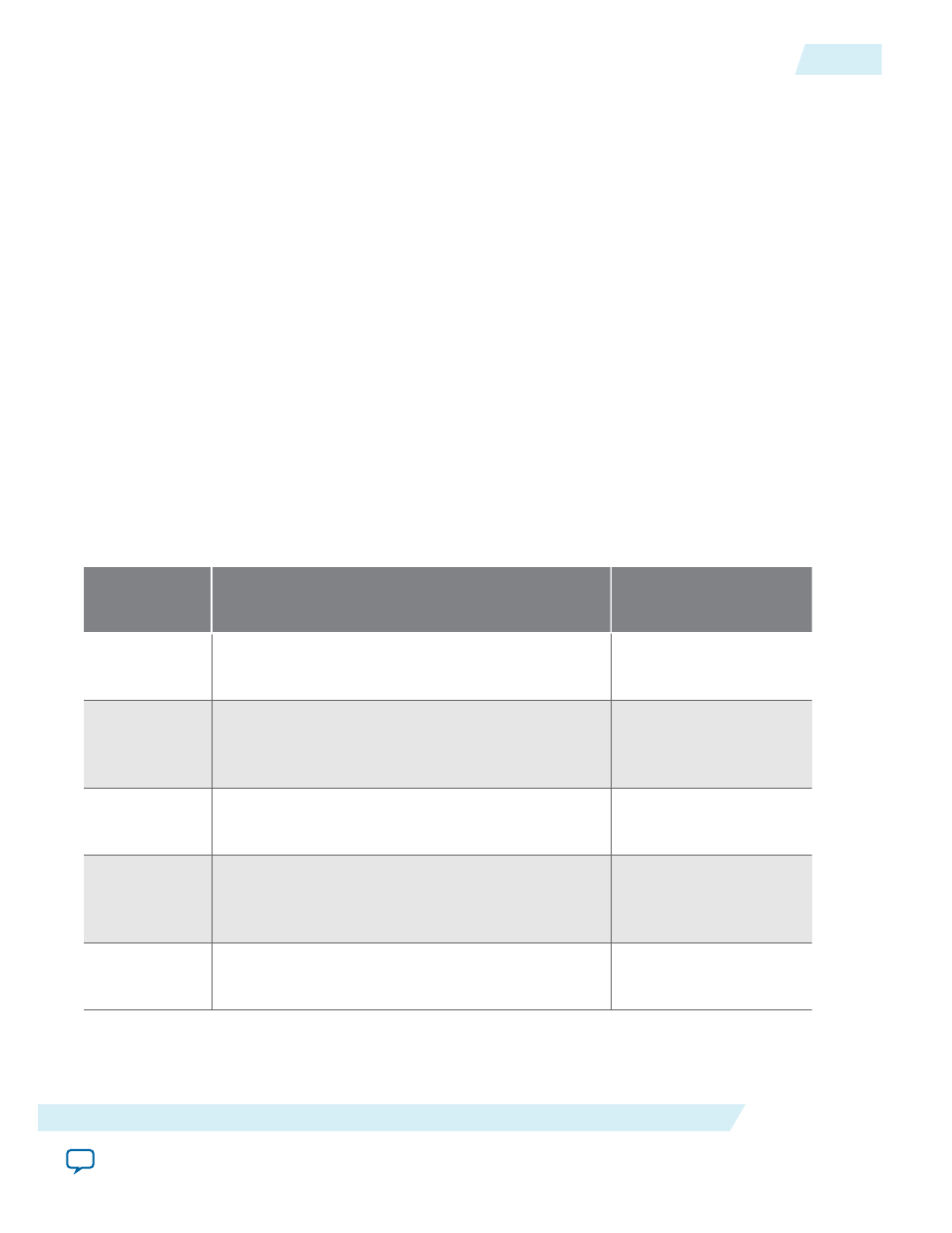

Table 13-2: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

v14.0.0

-Removed mention of SOPC Builder, updated to Qsys

Maintenance Release

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the Core

in SOPC Builder”, and “Referenced Documents”

sections.

—

July 2010

v10.0.0

No change from previous release.

—

November

2009

v9.1.0

Added a description to specify the shift direction.

—

March 2009

v9.0.0

Added description of a new parameter, Number of

synchronizer stages: Depth.

—

UG-01085

2014.24.07

Limitations

13-3

Avalon-ST Serial Peripheral Interface Core

Altera Corporation