Interrupt detector, Component interface, Component parameterization – Altera Embedded Peripherals IP User Manual

Page 333: Interrupt detector -5, Component interface -5, Component parameterization -5

Interrupt Detector

The interrupt detector can be customized to detect either signal edges or pulse using the Qsys interface.

The interrupt detector generates an enable signal to start and stop the 32-bit counter.

Component Interface

Altera Interrupt Latency Calculator has an Avalon-MM slave interface which communicates with the

Interrupt service routine initiator.

The table below shows the component interface that is available on the Altera Interrupt Latency Counter

IP.

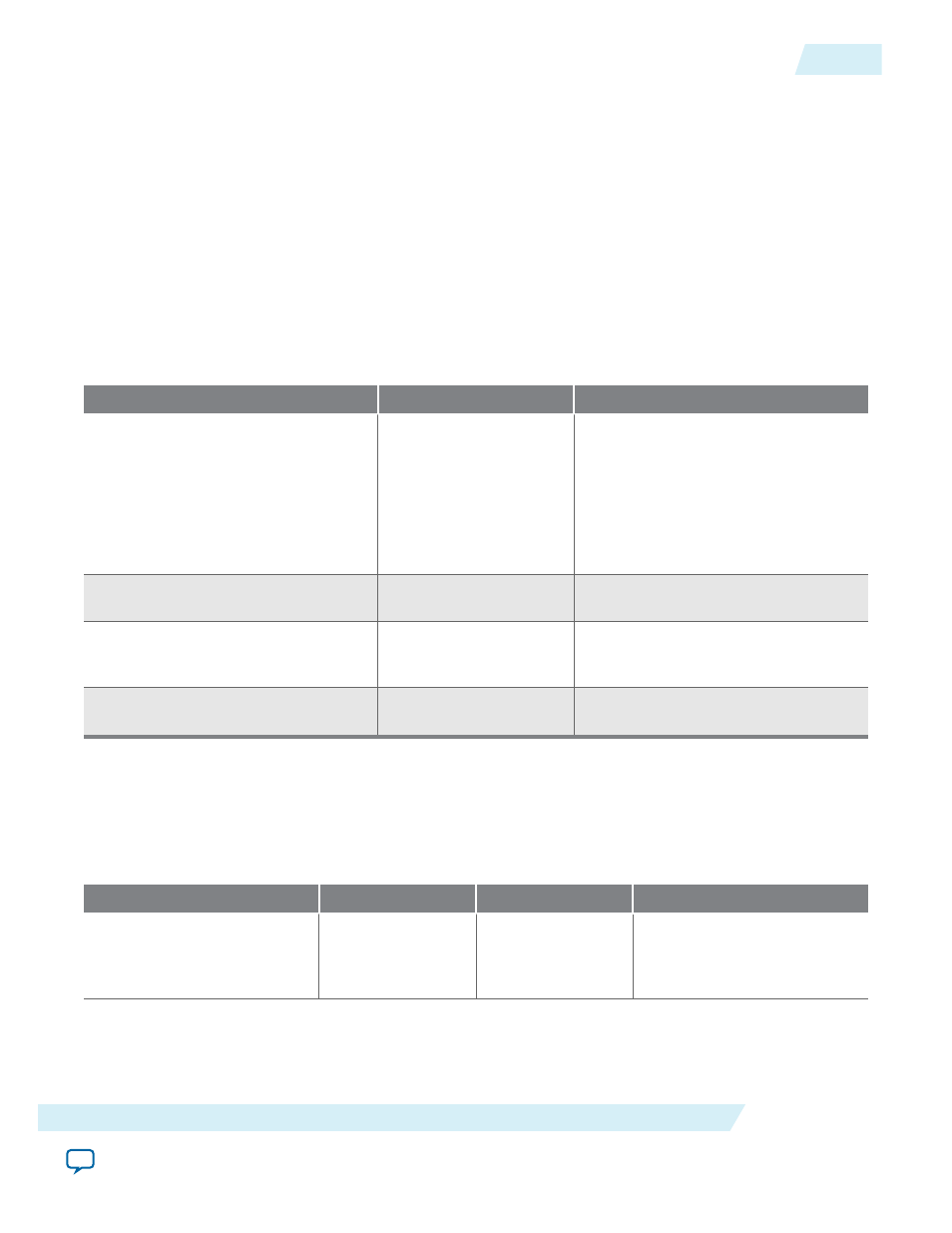

Table 34-7: Available Component Interfaces

Interface Port

Description

Remarks

Avalon-MM Slave (address , write,

waitrequest , writedata[31:0], read,

readdata[31:0])

Avalon-MM Slave

interface for processor to

talk to the IP.

This Avalon-MM slave interface

observes zero cycles read latency with

waitrequest signal. The waitrequest

signal defaults to binary ‘1’ if there is

no ongoing operation. If the Avalon-

MM Read or Write signal goes high,

the waitrequest signal only goes low if

the readdata_valid_register goes high.

Clock

Clock input of component. Clock signal to feed the latecy counter

logics.

Reset_n

Active LOW reset input/s. Support asynchronous reset assertion.

De-assertion of reset has to be

synchronized to the input clock.

IRQ

IRQ signal from the

interrupt signal initiator

Interrupt assertion and deassertion is

synchronized to input clock.

Component Parameterization

The table below shows the configuration parameters available on the Altera Interrupt Latency Counter IP.

Table 34-8: Available Component Parameterizations

Parameter Name

Description

Default Value

Allowable Range

CLOCK_RATE

Shows the frequency

of the clock signal

that is connected to

the IP

0

0 – 2^32

UG-01085

2014.24.07

Interrupt Detector

34-5

Altera Interrupt Latency Counter

Altera Corporation