Avalon-mm ports, Prefetchable avalon-mm master, Non-prefectchable avalon-mm master – Altera Embedded Peripherals IP User Manual

Page 137: Avalon-mm ports -3, Prefetchable avalon-mm master -3, Non-prefectchable avalon-mm master -3

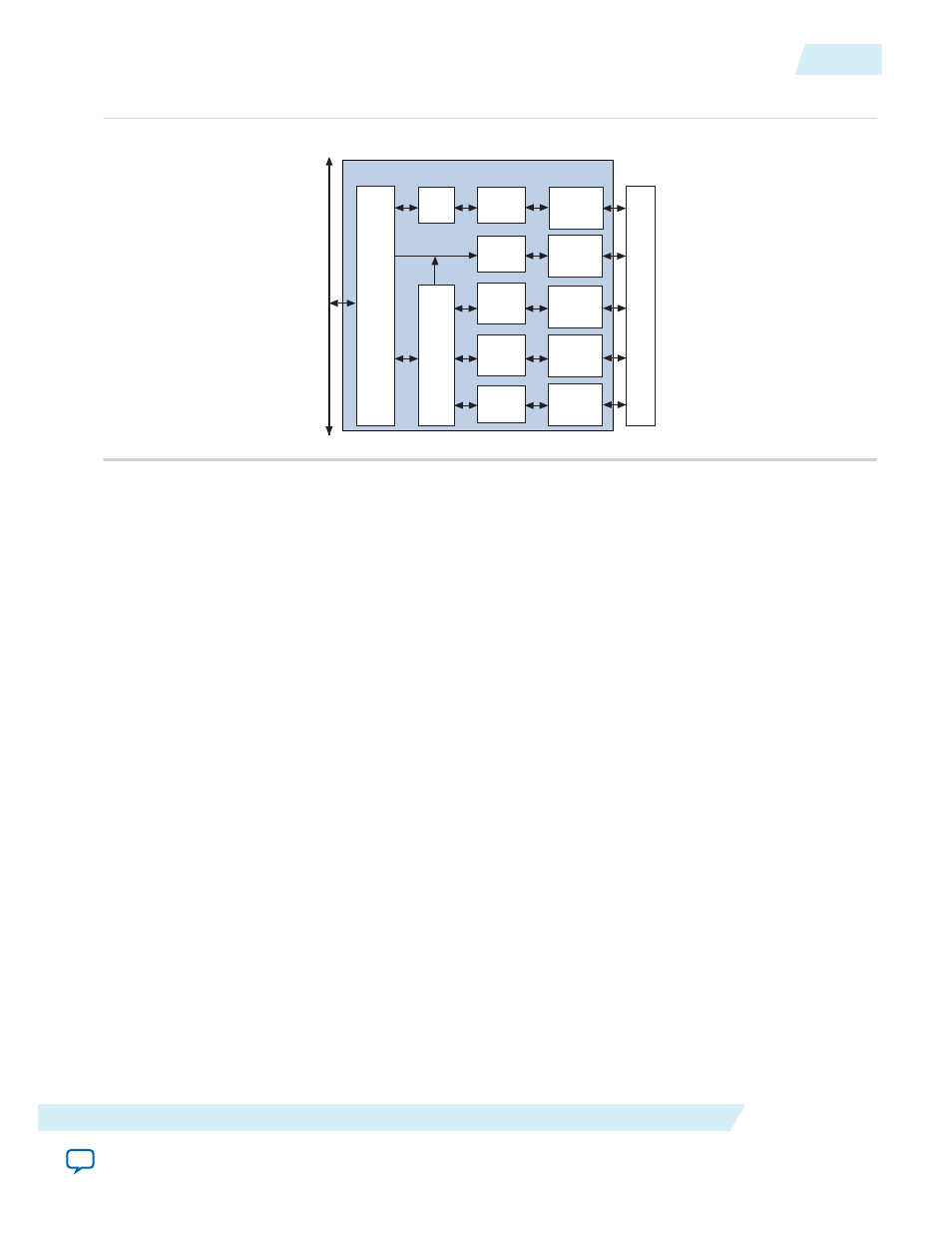

Figure 14-1: Generic PCI-Avalon Bridge Block Diagram

PCI Lite Core

Control

Register

Access

Avalon

Slave

Control

Status

Registers

PCI

Prefetchable

Bridge

Logic

PCI

Non-

Prefetchable

Bridge Logic

PCI

Bus

PCI

Master

Controller

Master

Bridge

Logic

PCI Bus

Access

Slave

Prefetchable

Avalon

Master

Non-

Prefetchable

Avalon

Master

I/O

Bridge

Logic

I/O

Avalon

Master

A

valon Switch

Fab

ric

PCI-Avalon Bridge

PCI

Target Controller

Avalon-MM Ports

The Avalon bridge comprises up to five predefined ports to communicate with the interconnect

(depending on device operating mode).

This section discusses the five Avalon-MM ports:

• Prefetchable Avalon-MM master

• Non-Prefetchable Avalon-MM master

• I/O Avalon-MM master

• PCI bus access slave

• Control register access (CRA) Avalon-MM slave

Prefetchable Avalon-MM Master

The prefetchable Avalon-MM master port provides a high bandwidth PCI memory request access to

Avalon-MM slave peripherals. This master port is capable of generating Avalon-MM burst transactions

for PCI requests that hit a prefetchable base address register (BAR). You should only connect prefetchable

Avalon-MM slaves to this port, typically RAM or ROM memory devices.

This port is optimized for high bandwidth transfers as a PCI target and it does not support single cycle

transactions.

Non-Prefectchable Avalon-MM Master

The Non-Prefetchable Avalon-MM master port provides a low latency PCI memory request access to

Avalon-MM slave peripherals. Burst operations are not supported on this master port. Only the exact

amount of data needed to service the initial data phase is read from the interconnect. Therefore, the PCI

byte enables (for the first data phase of the PCI read transaction) are passed directly to the interconnect.

UG-01085

2014.24.07

Avalon-MM Ports

14-3

PCI Lite Core

Altera Corporation