Altera_vic_driver..irq_ril, Altera_vic_driver..irq_rnmi – Altera Embedded Peripherals IP User Manual

Page 290

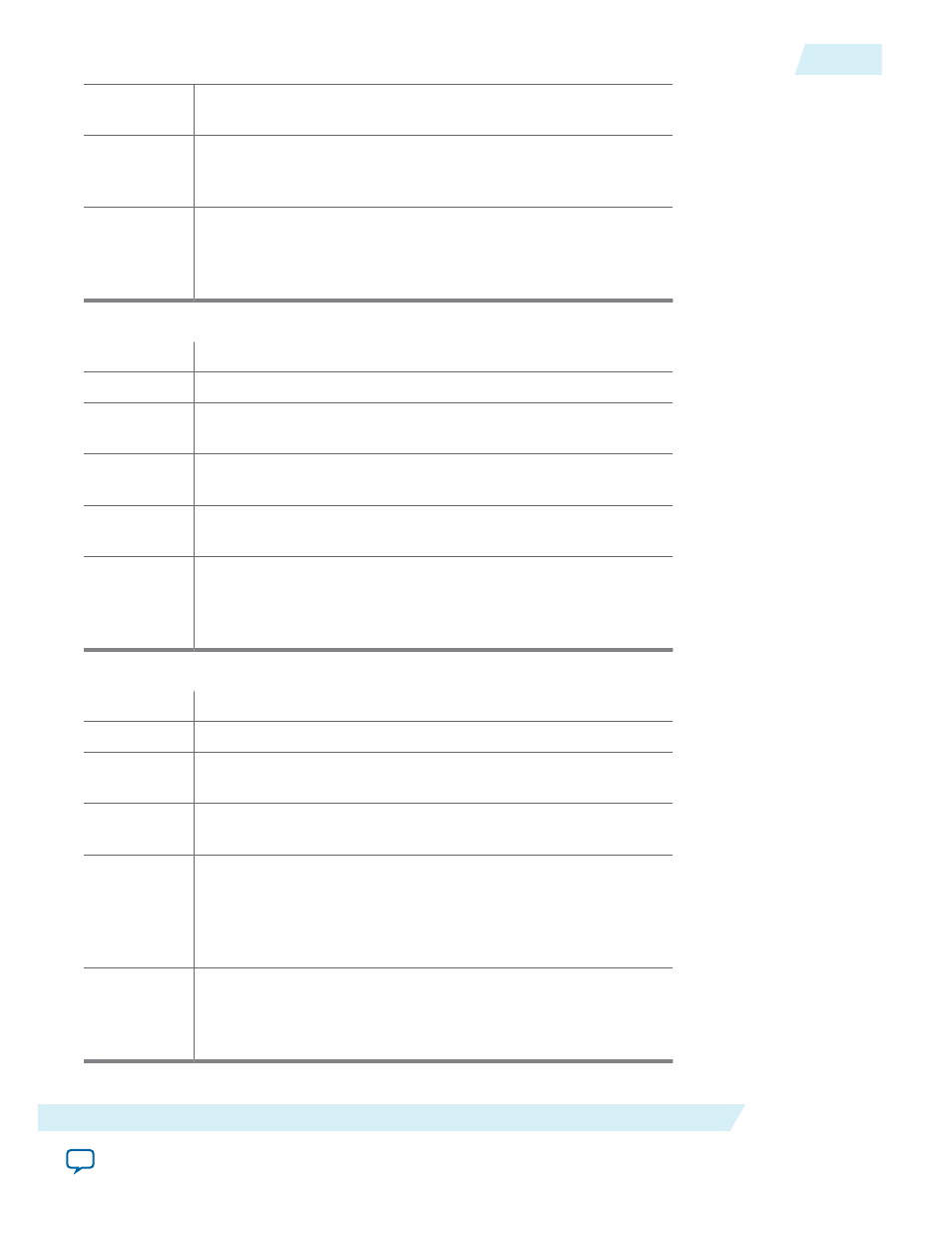

Destina‐

tion file:

system.h

Descrip‐

tion:

Specifies the RRS for the interrupt connected to the

corresponding port. Legal values are 1 to the number of shadow

register sets defined for the processor.

Occurs:

Per IRQ per instance;

refers to the IRQ number that you assign in SOPC Builder. Refer

to SOPC Builder to determine which IRQ numbers correspond

to which components in your design.

altera_vic_driver.

Identifier: ALTERA_VIC_DRIVER_

Type:

DecimalNumber

Default

value:

Refer to Default Settings for RRS and RIL section.

Destina‐

tion file:

system.h

Descrip‐

tion:

Specifies the RIL for the interrupt connected to the

corresponding port. Legal values are 0 to 2RIL width -1.

Occurs:

Per IRQ per instance;

refers to the IRQ number that you assign in SOPC Builder. Refer

to SOPC Builder to determine which IRQ numbers correspond

to which components in your design.

altera_vic_driver.

Identifier: ALTERA_VIC_DRIVER_

Type:

Boolean

Default

value:

0

Destina‐

tion file:

system.h

Descrip‐

tion:

Specifies whether the interrupt port is a maskable or non-

maskable interrupt (NMI). Legal values are 0 and 1. When set to

0, the port is maskable. NMIs cannot be disabled in hardware

and there are several restrictions imposed for the RIL and RRS

settings associated with any interrupt with NNI enabled.

Occurs:

Per IRQ per instance;

refers to the IRQ number that you assign in SOPC Builder. Refer

to SOPC Builder to determine which IRQ numbers correspond

to which components in your design.

UG-01085

2014.24.07

altera_vic_driver.

28-21

Vectored Interrupt Controller Core

Altera Corporation