Parameters, Parameters -9 – Altera Embedded Peripherals IP User Manual

Page 200

Parameters

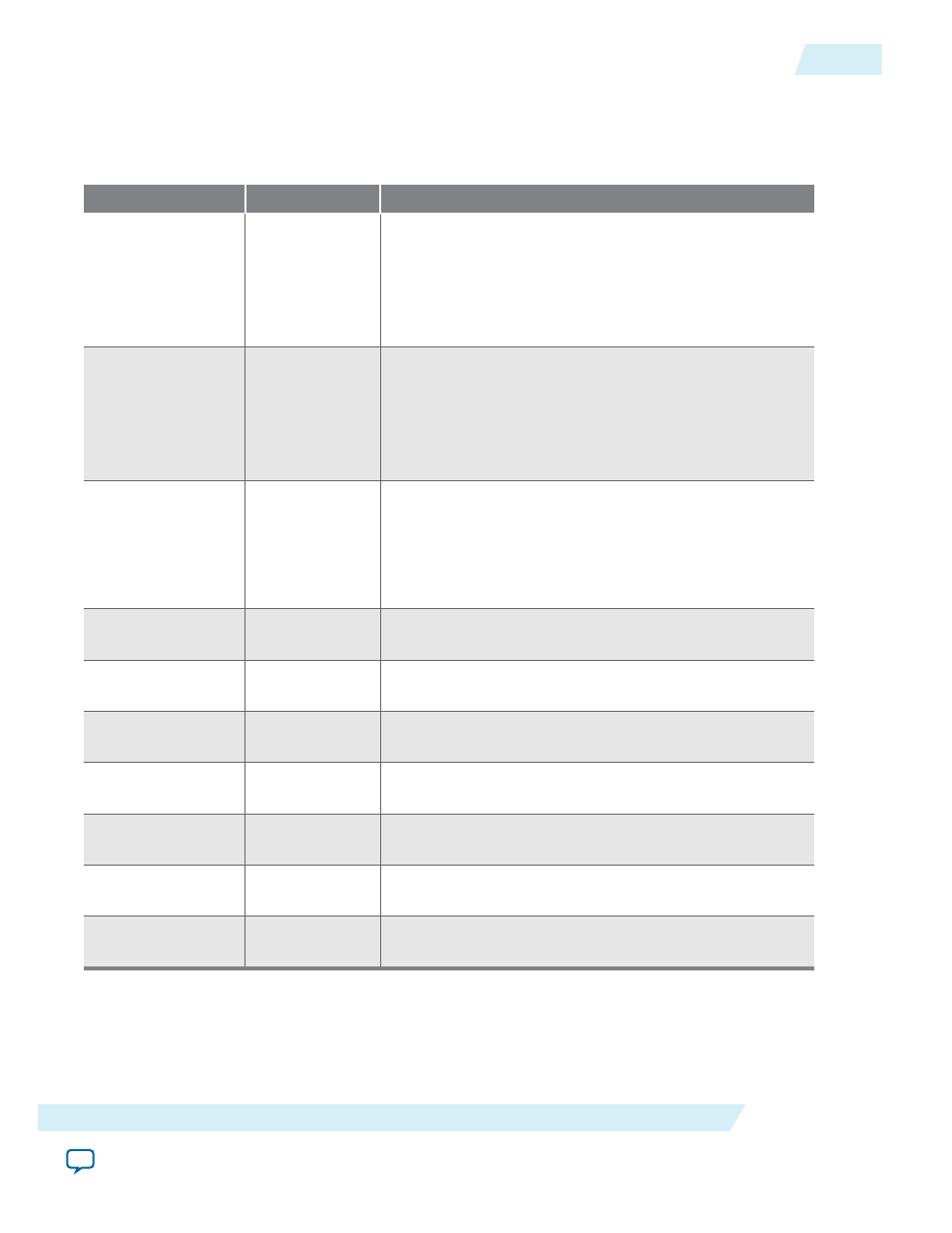

Table 21-5: Configurable Parameters

Parameter

Legal Values

Description

Transfer mode

Memory To

Memory

Memory To

Stream

Stream To

Memory

Configuration to use. For more information about these

configurations, see the Memory-to-Memory Configura‐

tion section.

Enable bursting

on descriptor read

master

On/Off

If this option is on, the descriptor processor block uses

Avalon-MM bursting when fetching descriptors and

writing them back in memory. With 32-bit read and write

ports, the descriptor processor block can fetch the 256-bit

descriptor by performing 8-word burst as opposed to

eight individual single-word transactions.

Allow unaligned

transfers

On/Off

If this option is on, the core allows accesses to non-word-

aligned addresses. This option doesn’t apply for burst

transfers.

Unaligned transfers require extra logic that may

negatively impact system performance.

Enable burst

transfers

On/Off

Turning on this option enables burst reads and writes.

Read burstcount

signal width

1–16

The width of the read

burstcount

signal. This value

determines the maximum burst read size.

Write burstcount

signal width

1–16

The width of the write

burstcount

signal. This value

determines the maximum burst write size.

Data width

8, 16, 32, 64

The data width in bits for the Avalon-MM read and write

ports.

Source error

width

0–7

The width of the

error

signal for the Avalon-ST source

port.

Sink error width 0 – 7

The width of the

error

signal for the Avalon-ST sink

port.

Data transfer

FIFO depth

2, 4, 8, 16, 32, 64 The depth of the internal data FIFO in memory-to-

memory configurations with burst transfers disabled.

The SG-DMA controller core should be given a higher priority (lower IRQ value) than most of the

components in a system to ensure high throughput.

UG-01085

2014.24.07

Parameters

21-9

Scatter-Gather DMA Controller Core

Altera Corporation