Document revision history, Document revision history -8 – Altera Embedded Peripherals IP User Manual

Page 181

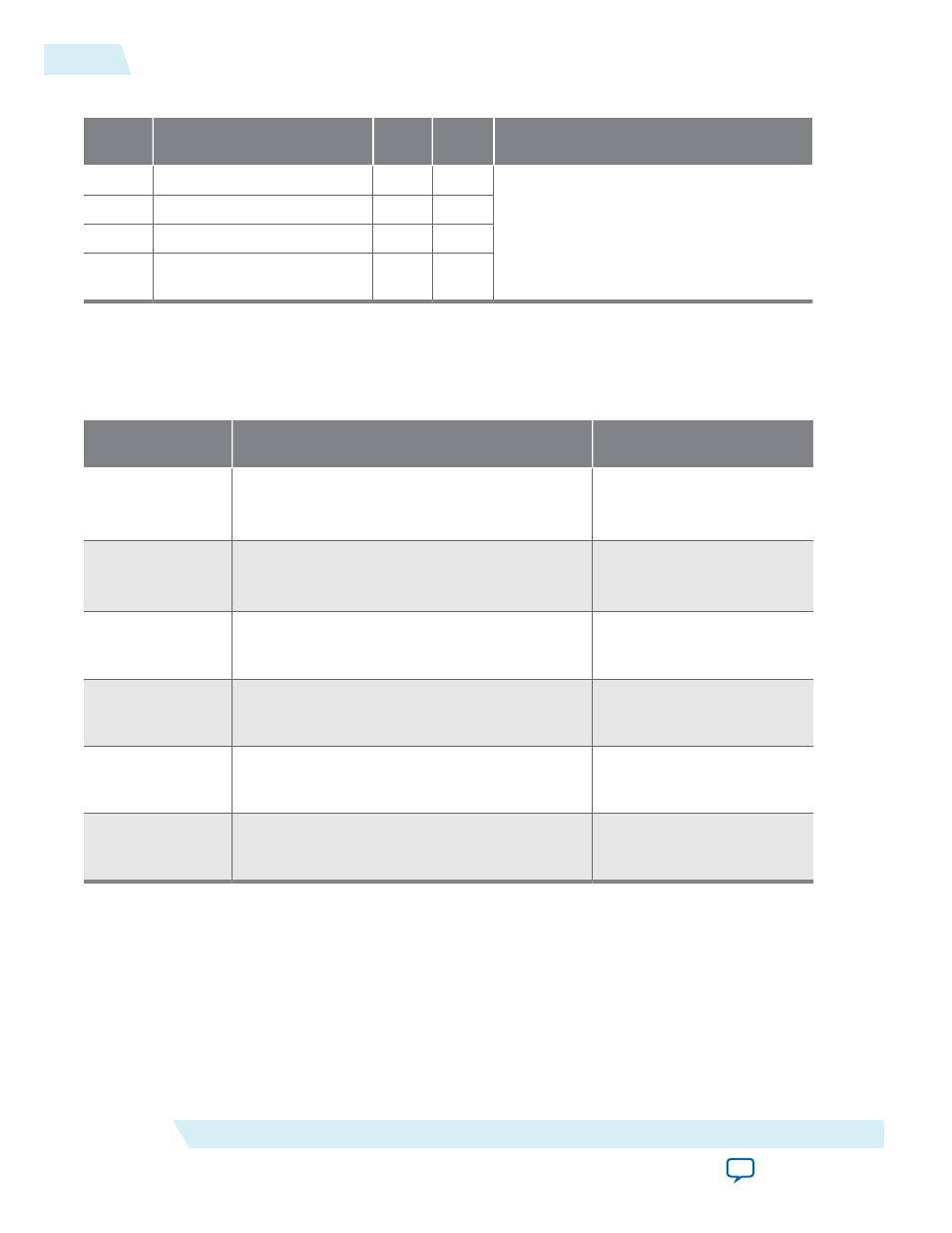

Table 17-7: Fill-level Interface Register Map

Byte

Offset

Name

Access

Reset

Value

Description

0

fill_level_0

RO

0

Fill level for each channel. Each register is

defined for each channel. For example, if

the core is configured to support four

channel, four fill-level registers are

defined.

4

fill_level_1

RO

0

8

fill_level_2

RO

0

(n*4

)

fill_level_n

RO

0

Document Revision History

Table 17-8: Document Revision History

Date and Document

Version

Changes Made

Summary of Changes

December 2010

v10.1.0

Removed the “Device Support”, “Instantiating the

Core in SOPC Builder”, and “Referenced

Documents” sections.

—

July 2010

v10.0.0

Added the description of almost-empty thresholds

and fill-level registers. Revised the Operation

section.

—

November 2009

v9.1.0

No change from previous release.

—

March 2009

v9.0.0

No change from previous release.

—

November 2008

v8.1.0

Changed to 8-1/2 x 11 page size. No change to

content.

—

May 2008

v8.0.0

Initial release.

—

17-8

Document Revision History

UG-01085

2014.24.07

Altera Corporation

Avalon-ST Multi-Channel Shared Memory FIFO Core