Slave mode operation, Multi-slave environments – Altera Embedded Peripherals IP User Manual

Page 110

for each active edge of

sclk

. The SPI core divides the Avalon-MM system clock using a clock divider to

generate the

sclk

signal.

When the SPI core is configured to interface with multiple slaves, the core has one

ss_n

signal for each

slave. During a transfer, the master asserts

ss_n

to each slave specified in the

slaveselect

register. Note

that there can be no more than one slave transmitting data during any particular transfer, or else there will

be a contention on the

miso

input. The number of slave devices is specified at system generation time.

Slave Mode Operation

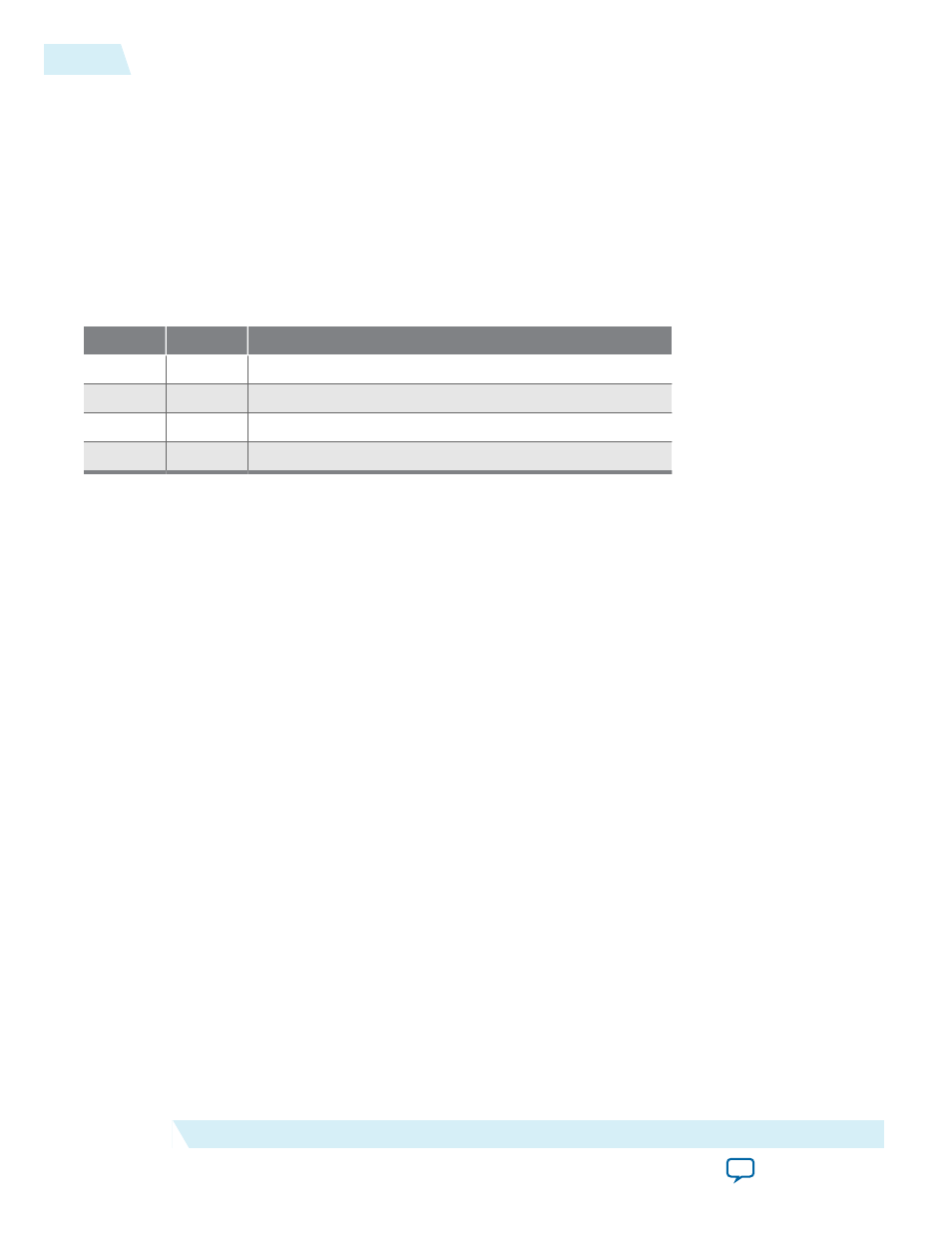

In slave mode, the SPI ports behave as shown in the table below.

Table 10-2: Slave Mode Port Configurations

Name

Direction

Description

mosi

input

Data input from the master

miso

output

Data output to the master

sclk

input

Synchronization clock

ss_n

input

Select signal

In slave mode, the SPI core simply waits for the master to initiate transactions. Before a transaction

begins, the slave logic continuously polls the

ss_n

input. When the master asserts

ss_n

, the slave logic

immediately begins sending the transmit shift register contents to the

miso

output. The slave logic also

captures data on the

mosi

input, and fills the receive shift register simultaneously. After a word is received

by the slave, the master must de-assert the

ss_n

signal and reasserts the signal again when the next word is

ready to be sent.

An intelligent host such as a microprocessor writes data to the

txdata

registers, so that it is transmitted

the next time the master initiates an operation. A master peripheral reads received data from the

rxdata

register. A master peripheral can enable interrupts to notify the host whenever new data is received, or

whenever the transmit buffer is ready for new data.

Multi-Slave Environments

When

ss_n

is not asserted, typical SPI cores set their

miso

output pins to high impedance. The Altera

®

-

provided SPI slave core drives an undefined high or low value on its

miso

output when not selected.

Special consideration is necessary to avoid signal contention on the

miso

output, if the SPI core in slave

mode is connected to an off-chip SPI master device with multiple slaves. In this case, the

ss_n

input

should be used to control a tristate buffer on the

miso

signal.

10-4

Slave Mode Operation

UG-01085

2014.24.07

Altera Corporation

SPI Core