2 functional description – Altera Embedded Peripherals IP User Manual

Page 183

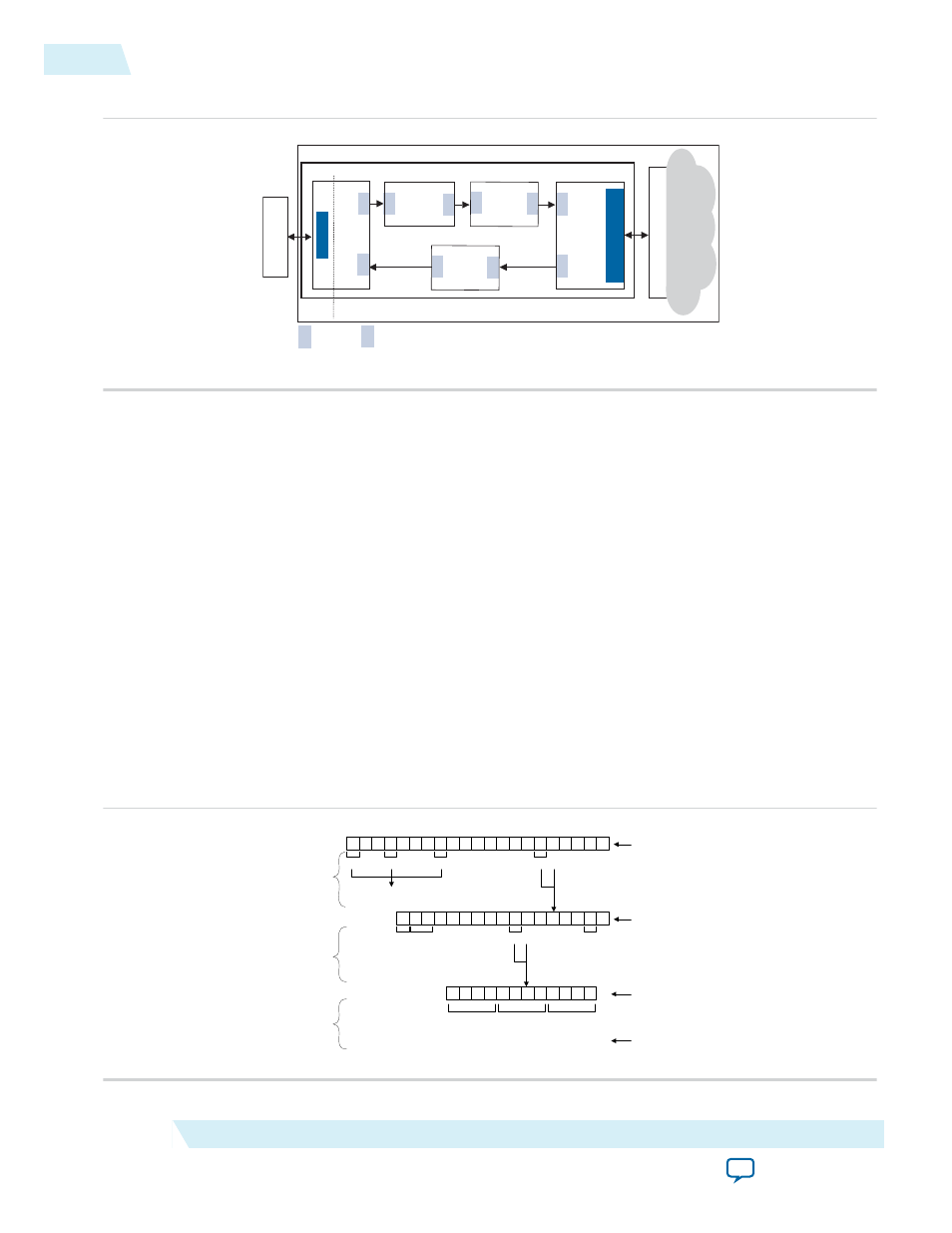

Figure 18-2: System with a JTAG to Avalon Master Bridge Core

a

F t

c

e

n

n

o

cr

et

nI

m

et

s

y

S

b

cir

Rest of the

System

Host

PC

Altera FPGA

JTAG to Transaction Bridge

src

k

ni

s

Avalon-ST

Bytes to

Packets

Converter

src

k

ni

s

Avalon-ST

Packets to

Transactions

Converter

A

v

alon-MM

src

Avalon-ST

Source

sink

Avalon-ST

Sink

src

k

ni

s

Avalon-ST

Single Clock

FIFO

(64 bytes)

src

k

ni

s

Avalon-ST

Packets to

Bytes

Converter

Avalon-ST

JTAG

Interface

Core

G

AT

J

src

k

ni

s

JTAG

Clock

JTAG

Clock

System

Clock

The SPI Slave to Avalon Master Bridge and the JTAG to Avalon Master Bridge cores accept encoded

streams of bytes with transaction data on their respective physical interfaces and initiate Avalon-MM

transactions on their Avalon-MM interfaces. Each bridge consists of the following cores, which are

available as stand-alone components in Qsys:

• Avalon-ST Serial Peripheral Interface and Avalon-ST JTAG Interface—Accepts incoming data in

bits and packs them into bytes.

• Avalon-ST Bytes to Packets Converter—Transforms packets into encoded stream of bytes, and a

likewise encoded stream of bytes into packets.

• Avalon-ST Packets to Transactions Converter—Transforms packets with data encoded according to

a specific protocol into Avalon-MM transactions, and encodes the responses into packets using the

same protocol.

• Avalon-ST Single Clock FIFO—Buffers data from the Avalon-ST JTAG Interface core. The FIFO is

only used in the JTAG to Avalon Master Bridge.

For the bridges to successfully transform the incoming streams of bytes to Avalon-MM transactions,

the streams of bytes must be constructed according to the protocols used by the cores.

The following example shows how a bytestream changes as it is transferred through the different layers

in the bridges.

Figure 18-3: Bits to Avalon-MM Transaction

00 00

00 04

7A 7C

00

02 4B

5A 40

7D

6A FF 03

5F

7B

4A

4A

4A

4D

00 00 00 04 02 4B 7A 40 4A FF 03 5F

Comma nd

Addres s

Dat a

Writes four bytes of data (4A, FF, 03 an d

5F) to a dd re ss 0x024 B7A40

Pa c ket Laye r

Input: Byte s

Outp ut: Ava lon-S T

P a cket s

Trans ac tio n Layer

Inp ut: Ava lon-S T

Pack e ts

Output: Ava lon-MM

Tran s a ction

00 00 00 04

7A 7C 00

02 4B

5A 40

7D

4A FF 03

5F

7B

LSB

MSB

Idle

Idle

Idle

Esca pe

Dropp e d

Esca pe is droppe d.

Ne xt byte is XORe d

with 0x20.

Phys ic al Laye r

Input: Bits

Output: Byte s

SO P Ch 0

Escap e

Esc a pe is drop pe d.

Next byte is XORed

with 0x20.

EO P

Bytes ca rried ove r

the phys ica l inte rfa ce

a fte r idle s a nd esc a pes

have be en inse rte d.

The p a cket enc ode d

as byt e s .

The tra ns ac tion

en ca ps ula ted a s a

pack e t.

The Ava lon-MM

tra nsact ion .

18-2

Functional Description

UG-01085

2014.24.07

Altera Corporation

SPI Slave/JTAG to Avalon Master Bridge Cores