Divisor register (optional), Endofpacket register (optional) – Altera Embedded Peripherals IP User Manual

Page 84

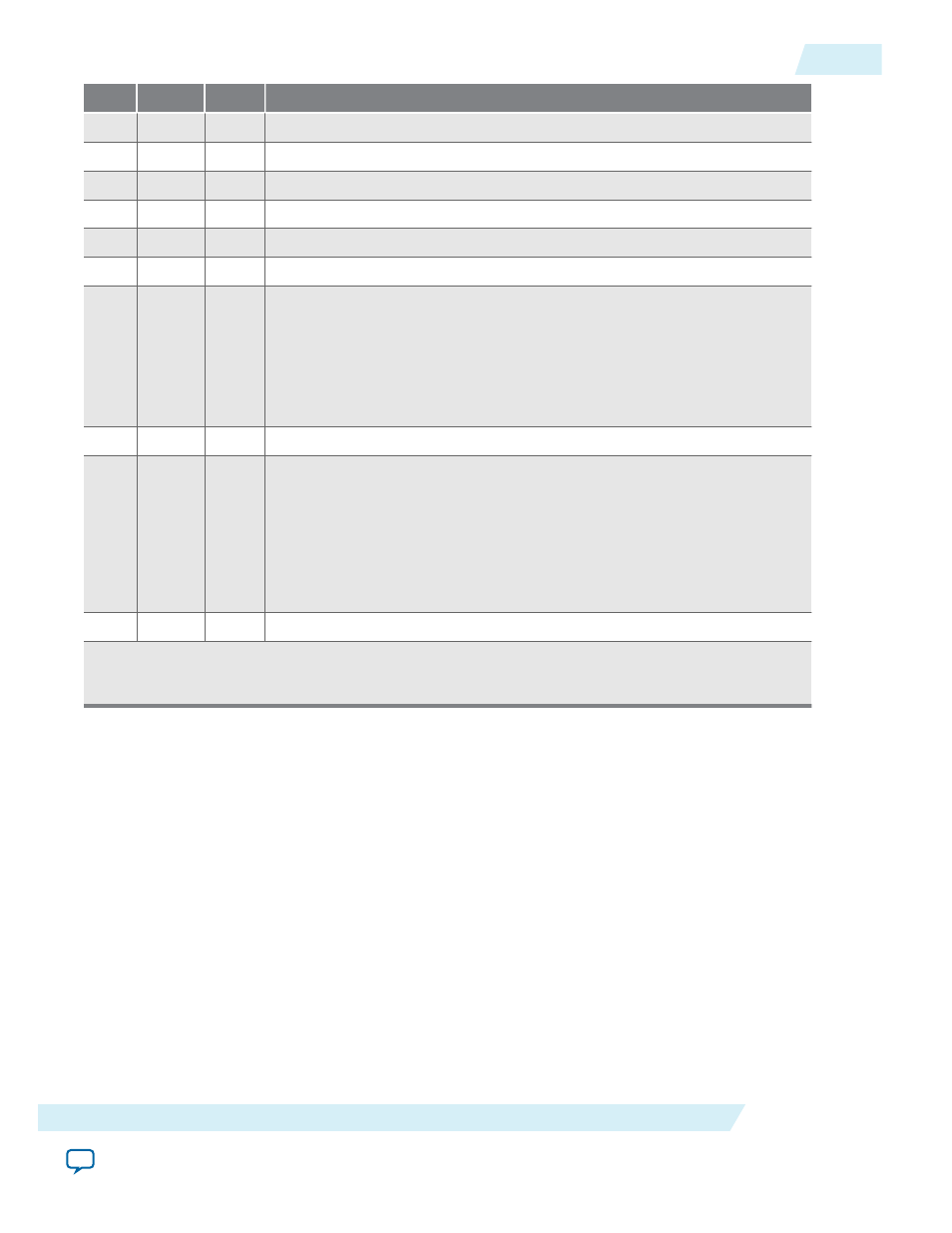

Bit

Name

Access

Description

3

IROE

RW

Enable interrupt for a receiver overrun error.

4

ITOE

RW

Enable interrupt for a transmitter overrun error.

5

ITMT

RW

Enable interrupt for a transmitter shift register empty.

6

ITRDY

RW

Enable interrupt for a transmission ready.

7

IRRDY

RW

Enable interrupt for a read ready.

8

IE

RW

Enable interrupt for an exception.

9

TRBK

RW

Transmit break. The

TRBK

bit allows an Avalon-MM master peripheral to

transmit a break character over the

TXD

output. The

TXD

signal is forced to

0 when the

TRBK

bit is set to 1. The

TRBK

bit overrides any logic level that

the transmitter logic would otherwise drive on the

TXD

output. The

TRBK

bit interferes with any transmission in process. The Avalon-MM master

peripheral must set the

TRBK

bit back to 0 after an appropriate break

period elapses.

10

IDCTS

RW

Enable interrupt for a change in

CTS

signal.

11

(1

)

RTS

RW

Request to send (

RTS

) signal. The

RTS

bit directly feeds the

RTS_N

output.

An Avalon-MM master peripheral can write the

RTS

bit at any time. The

value of the

RTS

bit only affects the

RTS_N

output; it has no effect on the

transmitter or receiver logic. Because the

RTS_N

output is logic negative,

when the

RTS

bit is 1, a low logic-level (0) is driven on the

RTS_N

output.

If the Flow Control hardware option is not enabled, the

RTS

bit always

reads 0, and writing has no effect. Refer to the Flow Control section.

12

IEOP

RW

Enable interrupt for end-of-packet condition.

Note

:

1. This bit is optional and may not exist in hardware.

divisor Register (Optional)

The value in the

divisor

register is used to generate the baud rate clock. The effective baud rate is

determined by the formula:

Baud Rate = (Clock frequency) / (divisor + 1)

The

divisor

register is an optional hardware feature. If the Baud Rate Can Be Changed By Software

hardware option is not enabled, the

divisor

register does not exist. In this case, writing

divisor

has no

effect, and reading

divisor

returns an undefined value. For more information, refer to the Baud Rate

Options section.

endofpacket Register (Optional)

The value in the

endofpacket

register determines the end-of-packet character for variable-length DMA

transactions. After reset, the default value is zero, which is the ASCII null character (\0). For more

information, refer to status Register bits for the description for the

EOP

bit.

UG-01085

2014.24.07

divisor Register (Optional)

8-15

UART Core

Altera Corporation