Msgdma interfaces and parameters, Component interface, Msgdma interfaces and parameters -4 – Altera Embedded Peripherals IP User Manual

Page 220

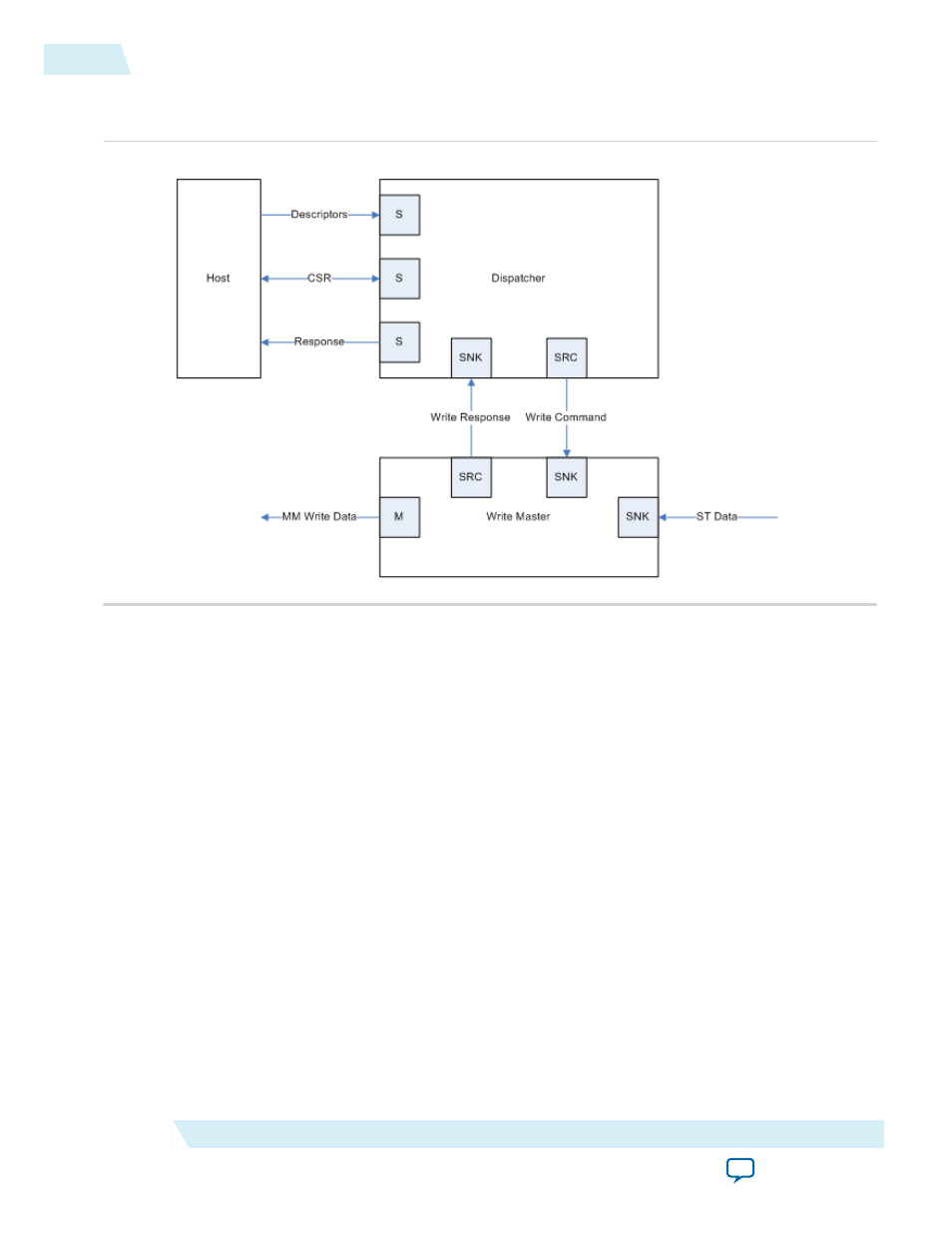

Figure 22-3: mSGDMA Module Configuration with Support for Avalon-ST Data Write Streaming to the

Memory-Mapped Bus.

Altera mSGDMA support 32-bit addressing by default. However, it can support 64-bit addressing when

you select enhanced feature in the dispatcher module GUI.

Besides the standard features of DMA operation requiring source and destination addresses, transfer size,

and optional interrupt generation; the Altera mSGDMA also supports extended features such as dynamic

burst count programming, stride addressing, extended discriptor format (64-bit addressing), and unique

sequence number identification for executed descriptor.

mSGDMA Interfaces and Parameters

Component Interface

The Altera mSGDMA component consists of one Avalon-MM CSR Slave port, one configurable Avalon-

MM Slave or Avalon-ST Source Response port, and the source and destination data path ports, it could be

Avalon-MM or Avalon-ST. The component also provides active high level interrupt output.

Only one clock domain can drive the mSGDMA. The requirement of different clock domains between

source and destination data paths are handled by the Qsys fabric.

A Hardware reset resets everything and a software reset resets the registers and FIFOs of the dispatchers

of the dispatcher and master modules. For a software reset, read the resetting bit of the status register to

determine when a full reset cycle has completed.

22-4

mSGDMA Interfaces and Parameters

UG-01085

2014.24.07

Altera Corporation

Altera Modular Scatter-Gather DMA