Software programming model, Hardware access routines, Software programming model -7 – Altera Embedded Peripherals IP User Manual

Page 113: Hardware access routines -7

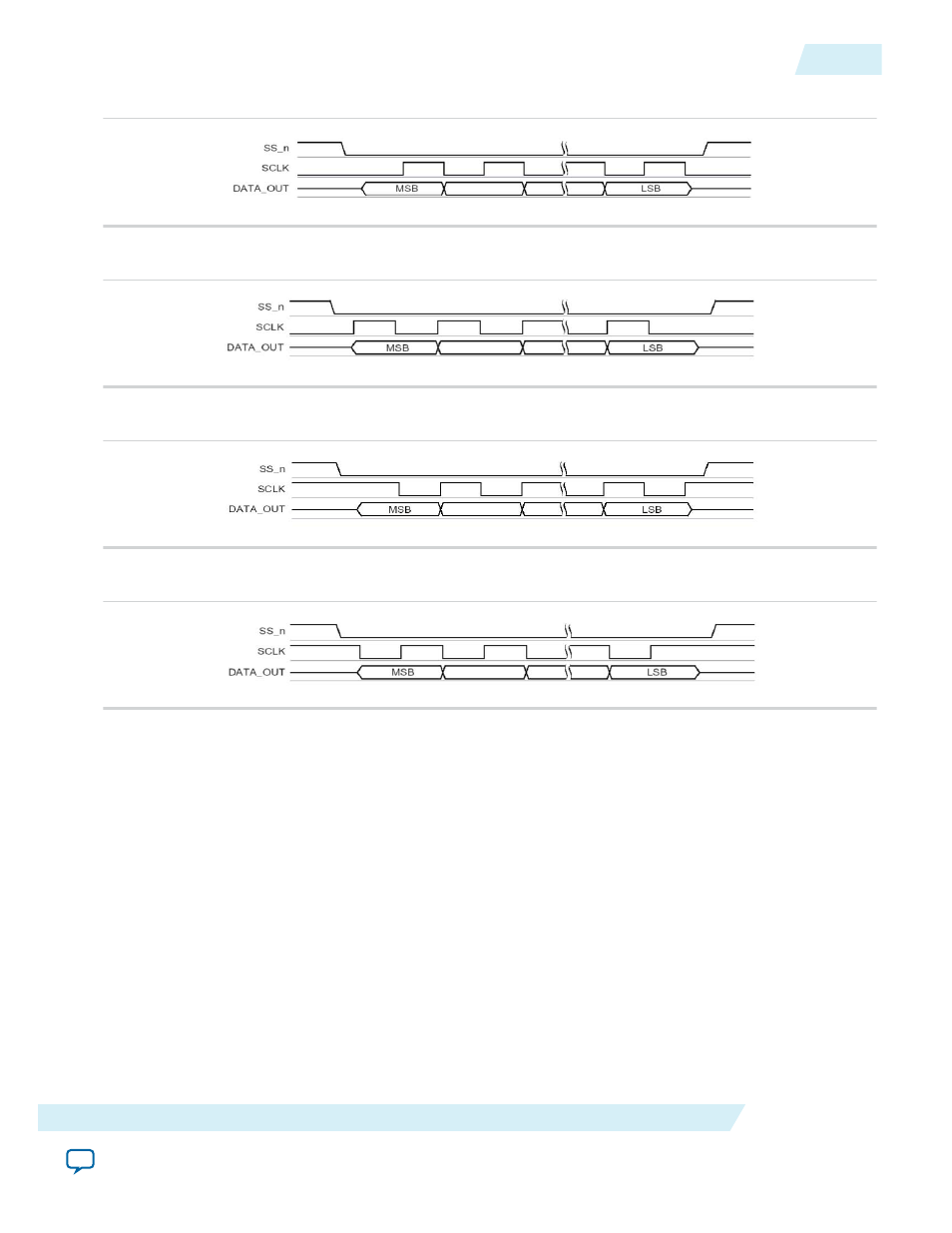

Figure 10-5: Clock Polarity = 0, Clock Phase = 0

Figure 10-6: Clock Polarity = 0, Clock Phase = 1

Figure 10-7: Clock Polarity = 1, Clock Phase = 0

Figure 10-8: Clock Polarity = 1, Clock Phase = 1

Software Programming Model

The following sections describe the software programming model for the SPI core, including the register

map and software constructs used to access the hardware. For Nios

®

II processor users, Altera provides

the HAL system library header file that defines the SPI core registers. The SPI core does not match the

generic device model categories supported by the HAL, so it cannot be accessed via the HAL API or the

ANSI C standard library. Altera provides a routine to access the SPI hardware that is specific to the SPI

core.

Hardware Access Routines

Altera provides one access routine,

alt_avalon_spi_command()

, that provides general-purpose access to

the SPI core that is configured as a master.

UG-01085

2014.24.07

Software Programming Model

10-7

SPI Core

Altera Corporation