Video sync generator and pixel converter cores, Core overview, Video sync generator – Altera Embedded Peripherals IP User Manual

Page 242: Functional description, Video sync generator and pixel converter cores -1, Core overview -1, Video sync generator -1, Functional description -1

Video Sync Generator and Pixel Converter

Cores

24

2014.24.07

UG-01085

Core Overview

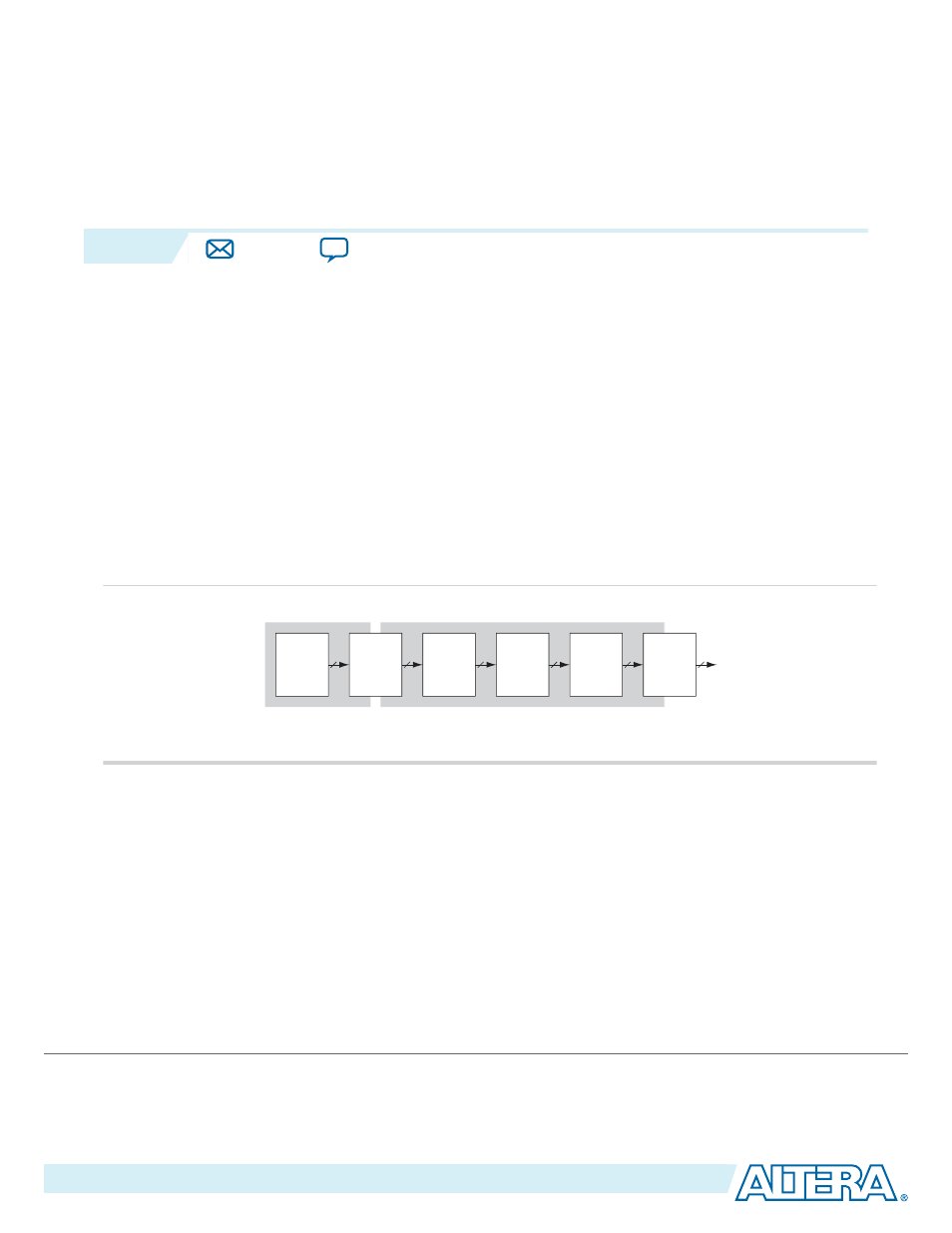

The video sync generator core accepts a continuous stream of pixel data in RGB format, and outputs the

data to an off-chip display controller with proper timing. You can configure the video sync generator core

to support different display resolutions and synchronization timings.

The pixel converter core transforms the pixel data to the format required by the video sync generator. The

Typical Placement in a System figure shows a typical placement of the video sync generator and pixel

converter cores in a system.

In this example, the video buffer stores the pixel data in 32-bit unpacked format. The extra byte in the

pixel data is discarded by the pixel converter core before the data is serialized and sent to the video sync

generator core.

Figure 24-1: Typical Placement in a System

Video

Buffer

SGDMA

FIFO

Pixel

Converter

Data

Format

Adapter

Video

Sync

Generator

32 bits

32 bits

32 bits

24 bits

8 bits

8 bits

0RGB

BGR0

BGR0

BGR

B,G,R

B,G,R

T

S

-

n

o

l

a

v

A

M

M

-

n

o

l

a

v

A

Video

Buffer

SGDMA

FIFO

Pixel

Converter

Data

Format

Adapter

Video

Sync

Generator

32 bits

32 bits

32 bits

24 bits

8 bits

8 bits

0RGB

BGR0

BGR0

BGR

B,G,R

B,G,R

T

S

-

n

o

l

a

v

A

M

M

-

n

o

l

a

v

A

These cores are deployed in the Nios II Embedded Software Evaluation Kit (NEEK), which includes an

LCD display daughtercard assembly attached via an HSMC connector.

Video Sync Generator

This section describes the hardware structure and functionality of the video sync generator core.

Functional Description

The video sync generator core adds horizontal and vertical synchronization signals to the pixel data that

comes through its Avalon

®

(Avalon-ST) input interface and outputs the data to an off-chip display

controller. No processing or validation is performed on the pixel data.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134