Avalon-to-pci read and write operation, Avalon-to-pci write request, Avalon-to-pci read and write operation -8 – Altera Embedded Peripherals IP User Manual

Page 142

Avalon-To-PCI Read and Write Operation

The PCI Bus Access Slave port is a burst-capable slave that attempts to create PCI bursts that match the

bursts requested from the interconnect.

The PCI-Avalon bridge is capable of handling bursts up to 512 bytes with a 32-bit PCI bus. In other

words, the maximum supported Avalon-MM burst count is 128.

Bursts from Avalon-MM can be received on any boundary. However, when internal PCI-Avalon bridge

bursts cross the Avalon-to-PCI address page boundary, they are broken into two pieces. Two bursts are

used because the address translation can change at that boundary, requiring a different PCI address for

the second portion of the burst with a burst count greater than 1.

Avalon-MM burst read requests are treated as if they are going to prefetchable PCI space. Therefore, if the

PCI target space is non-prefetchable, you should not use read bursts.

Several factors control how Avalon-MM transactions (bursts or single cycle) are translated to PCI transac‐

tions.

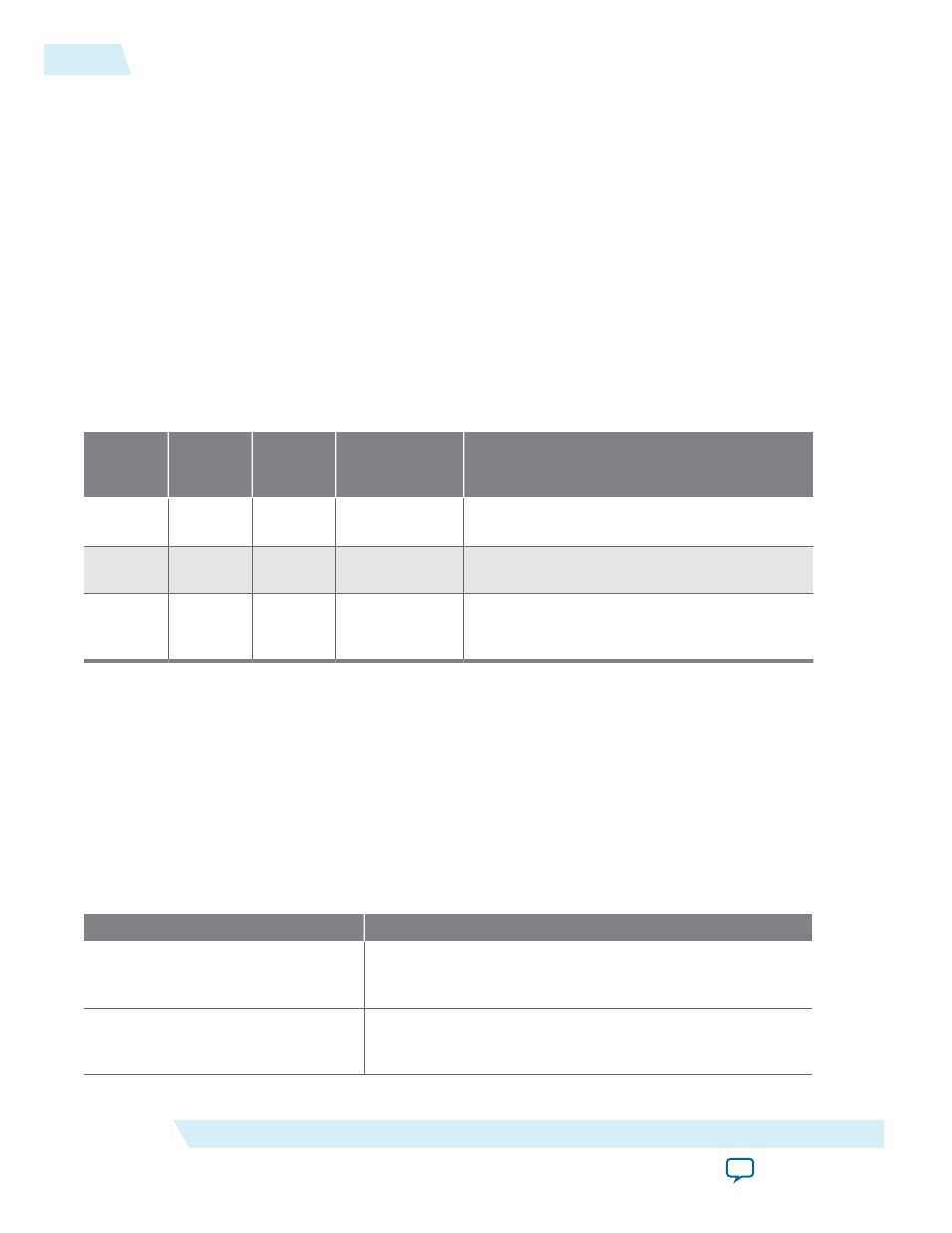

Table 14-6: Translation of Avalon Requests to PCI Requests

Data Path

Width

Avalon

Burst

Count

Type of

Operation

Avalon Byte

Enables

Resulting PCI Operation and Byte Enables

32

1

Read or

Write

Any value

Single data phase read or write, PCI byte

enables identical to Avalon byte enables

32

>1

Read

Any value

Attempt to burst on PCI. All data phases have

all PCI bytes enabled.

32

>1

Write

Any value

Attempt to burst on PCI. All data phases have

PCI byte enables identical to the Avalon byte

enables.

Avalon-to-PCI Write Request

For write requests from the interconnect, the write request is pushed onto the PCI bus as a configuration

write, I/O write, or memory write. When the Avalon-to-PCI command/write data buffer either has

enough data to complete the full burst or 8 data phases (32 bytes on a 32-bit PCI bus) are exceeded, the

PCI master controller issues the PCI write transaction.

The PCI write is issued to configuration, I/O, or memory space based on the address translation table. See

Avalon-to-PCI Address Translation section.

A PCI write burst can be terminated for various reasons.

Table 14-7: PCI Master Write Request Termination Conditions

Termination condition

Resulting Action

Burst count satisfied

Normal master-initiated termination on PCI bus, command

completes, and the master controller proceeds to the next

command.

Latency timer expiring during

configuration, I/O, or memory

write command

Normal master-initiated termination on PCI bus, the

continuation of the PCI write is requested from the master

controller arbiter.

14-8

Avalon-To-PCI Read and Write Operation

UG-01085

2014.24.07

Altera Corporation

PCI Lite Core