Software access, Routine for level sensitive interrupts, Routine for edge/pulse sensitive interrupts – Altera Embedded Peripherals IP User Manual

Page 334: Software access -6, Routine for level sensitive interrupts -6, Routine for edge/pulse sensitive interrupts -6

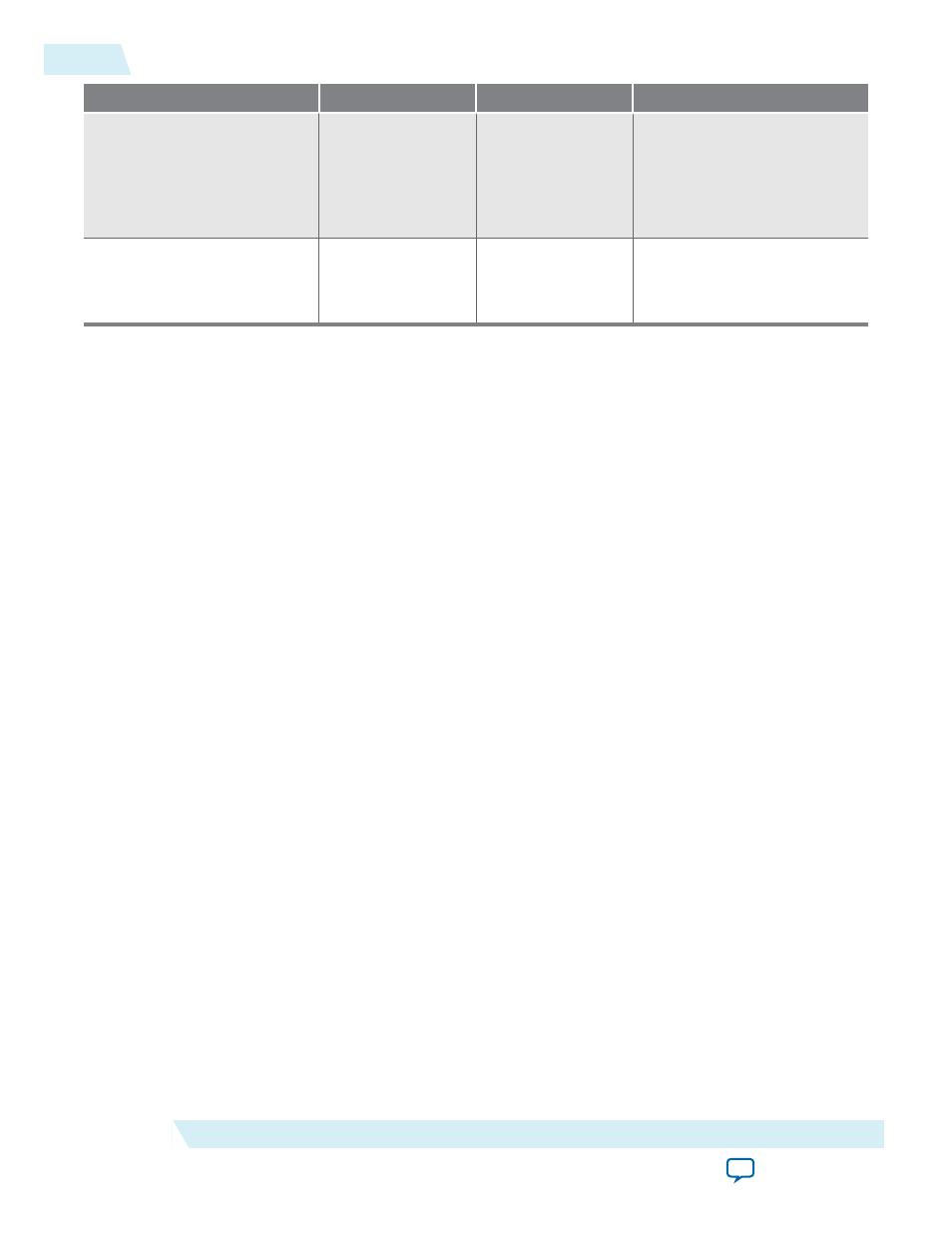

Parameter Name

Description

Default Value

Allowable Range

INTR_TYPE

Value 0: level

sensitive interrupt

input

Value 1: edge/pulse

interrupt input

0

0,1

IRQ_PORT_CNT

Allows user to

configure the

number of IRQ

PORT to use.

32

1 - 32

Software Access

Since the component supports two types of incoming interrupts - level and edge/pulse, the software access

routine for supporting each of the interrupt types has slightly different expectations.

Routine for Level Sensitive Interrupts

The software access routine for level sensitive interrupts is as follows:

1. Upon completion of ISR, read the data valid bit to ensure that the data is "valid" before reading the

interrupt latency counter.

2. Read from the Latency Data Register to obtain the actual cycle spend for the interrupt.

The value presented is in the amount of clock cycle associated with the clock connected to Interrupt

Latency Counter.

Routine for Edge/Pulse Sensitive Interrupts

The software access routine for edge/pulse sensitive interrupts is as follows:

1. Upon completion of ISR, or at the end of ISR, software needs to write binary ‘1’ to one of the 32-bit

registers of the Counter Stop Register to stop the internal counter from counting. The LSB represents

counter 0 and the MSB represents counter 31. This is the same as the level sensitive interrupt. Data

valid bit is recommended to be read before reading the latency counter.

2. Read from Latency Data Register to obtain the actual cycle spend for the interrupt. The counter stop

bit only needs clearing when the IP is configured to accept pulse IRQ. If level IRQ is employed. The

counter stop bit is ignored.

34-6

Software Access

UG-01085

2014.24.07

Altera Corporation

Altera Interrupt Latency Counter