Run-time initialization, Board support package, Run-time initialization -16 – Altera Embedded Peripherals IP User Manual

Page 285: Board support package -16

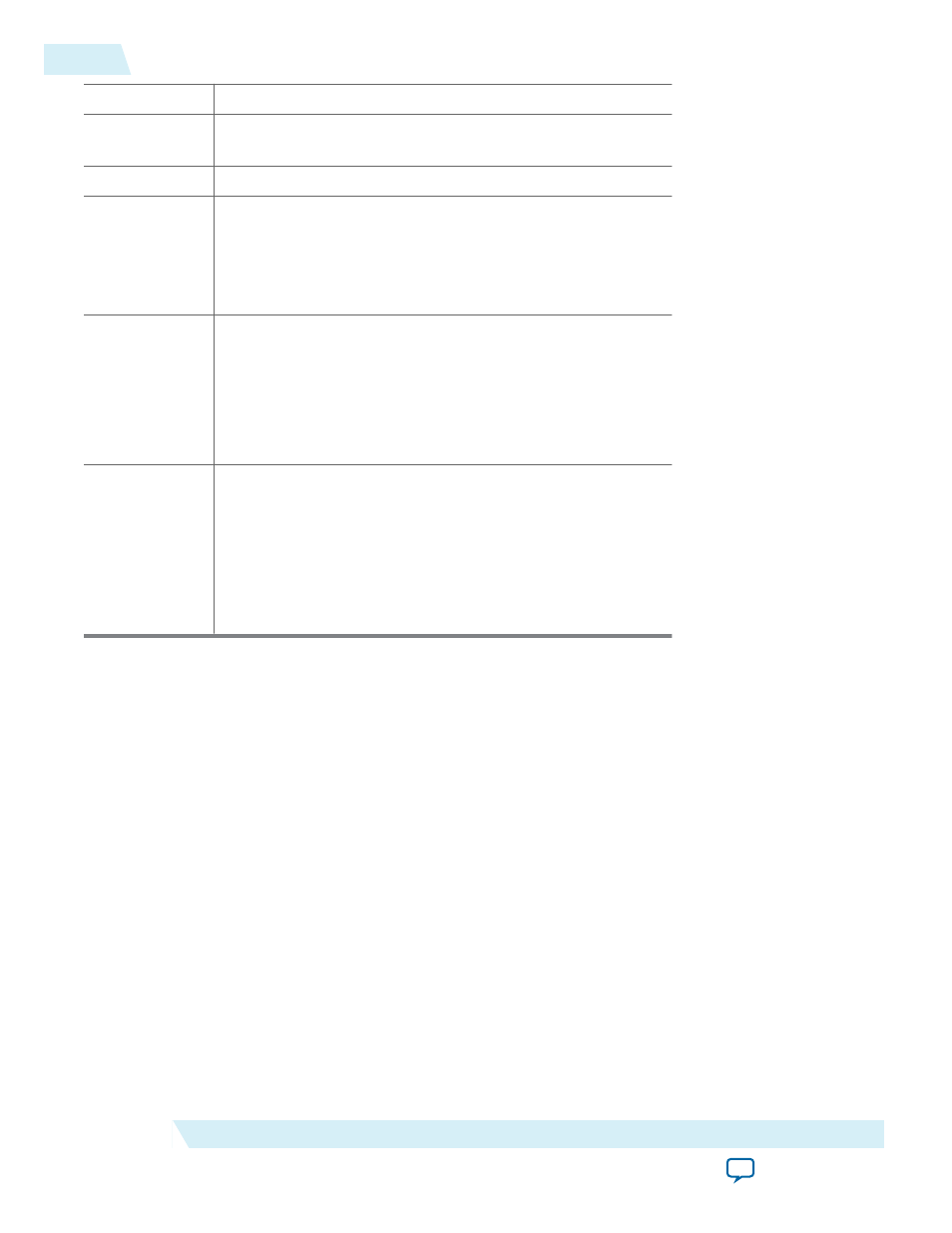

Thread-safe: No

Available

from ISR:

No

Include:

altera_vic_irq.h, altera_vic_regs.h

Parameters: ic_id—the interrupt controller identification number as

defined in

system.h

irq—the interrupt value as defined in

system.h

level—the interrupt level to set

Returns:

Returns zero if successful; otherwise non-zero for one or

more of the following reasons:

The value in ic_id is invalid

The value in irq is invalid

The value in level is invalid

Description: Sets the interrupt level for a single interrupt.

Altera recommends setting the interrupt level only to zero to

disable the interrupt or to the original value specified in your

BSP. Writing any other value could violate the overlapping

register set, priority level, and other design rules. Refer to the

VIC BSP Design Rules for Altera Hal Implementation

section for more information.

Run-time Initialization

During system initialization, software configures the each VIC instance's control registers using settings

specified in the BSP. The RIL, RRS, and RNMI fields are written into the interrupt configuration register

of each interrupt port in each VIC. All interrupts are disabled until other software registers a handler

using the alt_ic_isr_register() API.

Board Support Package

The BSP you generate for your Nios II system provides access to the hardware in your system, including

the VIC. The VIC driver includes scripts that the BSP generator calls to get default interrupt settings and

to validate settings during BSP generation. The Nios II BSP Editor provides a mechanism to edit these

settings and generate a BSP for your SOPC Builder design.

The generator produces a vector table file for each VIC in the system, named

altera_

along with other VIC driver source code. Its contents are based on the BSP settings for each VIC's

interrupt ports.

The VIC does not support runtime stack checking feature (hal.enable_runtime_stack_checking) in the

BSP setting.

28-16

Run-time Initialization

UG-01085

2014.24.07

Altera Corporation

Vectored Interrupt Controller Core