Accessing the jtag uart core via a host pc, Register map, Data register – Altera Embedded Peripherals IP User Manual

Page 66: Accessing the jtag uart core via a host pc -9, Register map -9

•

altera_avalon_jtag_uart_regs.h

—This file defines the core's register map, providing symbolic constants

to access the low-level hardware. The symbols in this file are used only by device driver functions.

•

altera_avalon_jtag_uart.h

,

altera_avalon_jtag_uart.c

—These files implement the HAL system library

device driver.

Accessing the JTAG UART Core via a Host PC

Host software is necessary for a PC to access the JTAG UART core. The Nios II IDE supports the JTAG

UART core, and displays character I/O in a console window. Altera also provides a command-line utility

called nios2-terminal that opens a terminal session with the JTAG UART core.

For further details, refer to the Nios II Software Developer's Handbook and Nios II IDE online help.

Register Map

Programmers using the HAL API never access the JTAG UART core directly via its registers. In general,

the register map is only useful to programmers writing a device driver for the core.

Note: The Altera-provided HAL device driver accesses the device registers directly. If you are writing a

device driver, and the HAL driver is active for the same device, your driver will conflict and fail to

operate.

The table below shows the register map for the JTAG UART core. Device drivers control and communi‐

cate with the core through the two, 32-bit memory-mapped registers.

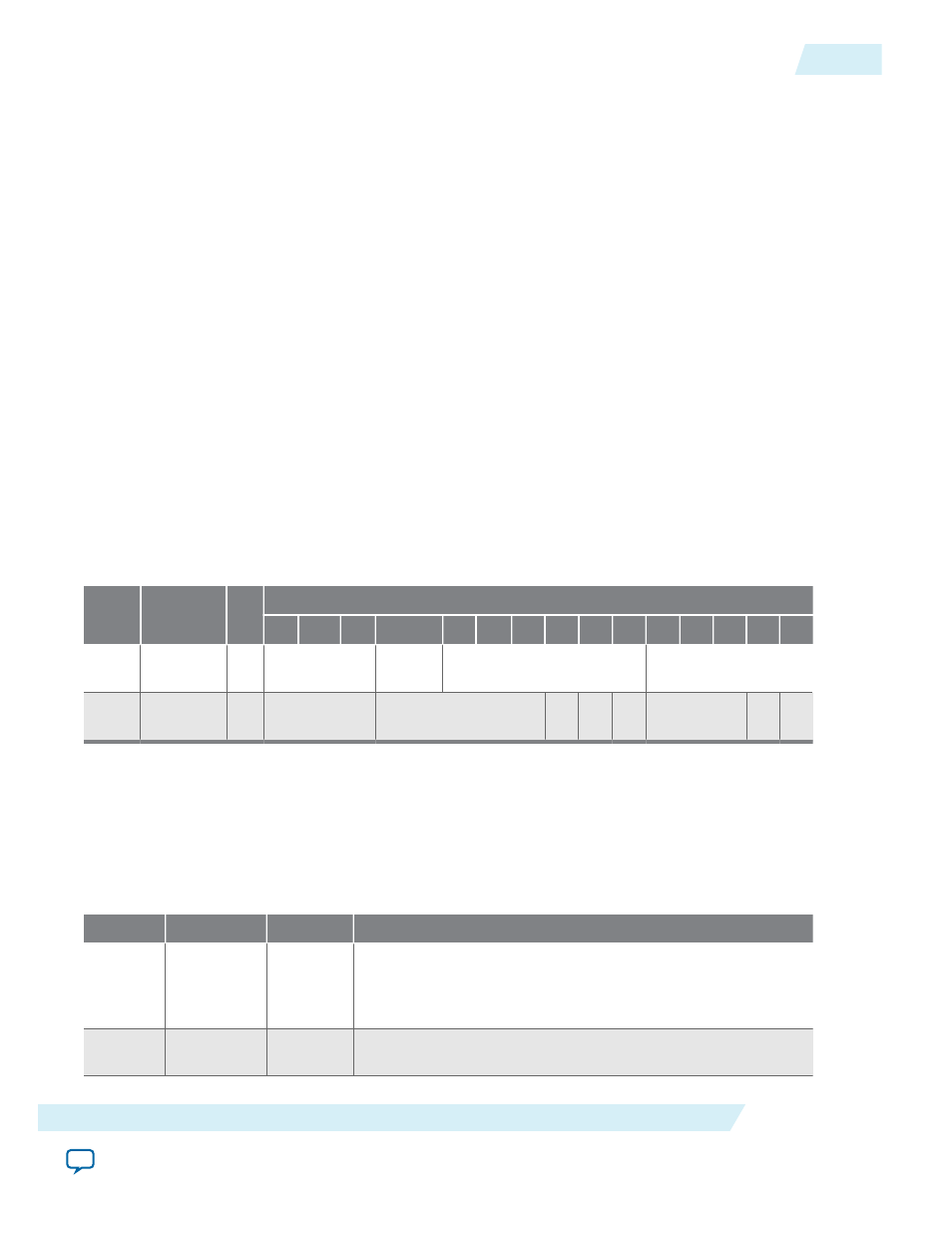

Table 7-4: JTAG UART Core Register Map

Offset

Register

Name

R/

W

Bit Description

31

...

16

15

14

...

11 10

9

8

7

...

2

1

0

0

data

R

W

RAVAIL

RVALID

Reserved

DATA

1

control

R

W

WSPACE

Reserved

AC

WI

RI

Reserved

WE

R

E

Note: Reserved fields—Read values are undefined. Write zero.

Data Register

Embedded software accesses the read and write FIFOs via the

data

register. The table below describes the

function of each bit.

Table 7-5: data Register Bits

Bit(s)

Name

Access

Description

[7:0]

DATA

R/W

The value to transfer to/from the JTAG core. When writing,

the

DATA

field holds a character to be written to the write

FIFO. When reading, the

DATA

field holds a character read

from the read FIFO.

[15]

RVALID

R

Indicates whether the

DATA

field is valid. If

RVALID

=1, the

DATA

field is valid, otherwise

DATA

is undefined.

UG-01085

2014.24.07

Accessing the JTAG UART Core via a Host PC

7-9

JTAG UART Core

Altera Corporation