Document revision history, Document revision history -13 – Altera Embedded Peripherals IP User Manual

Page 29

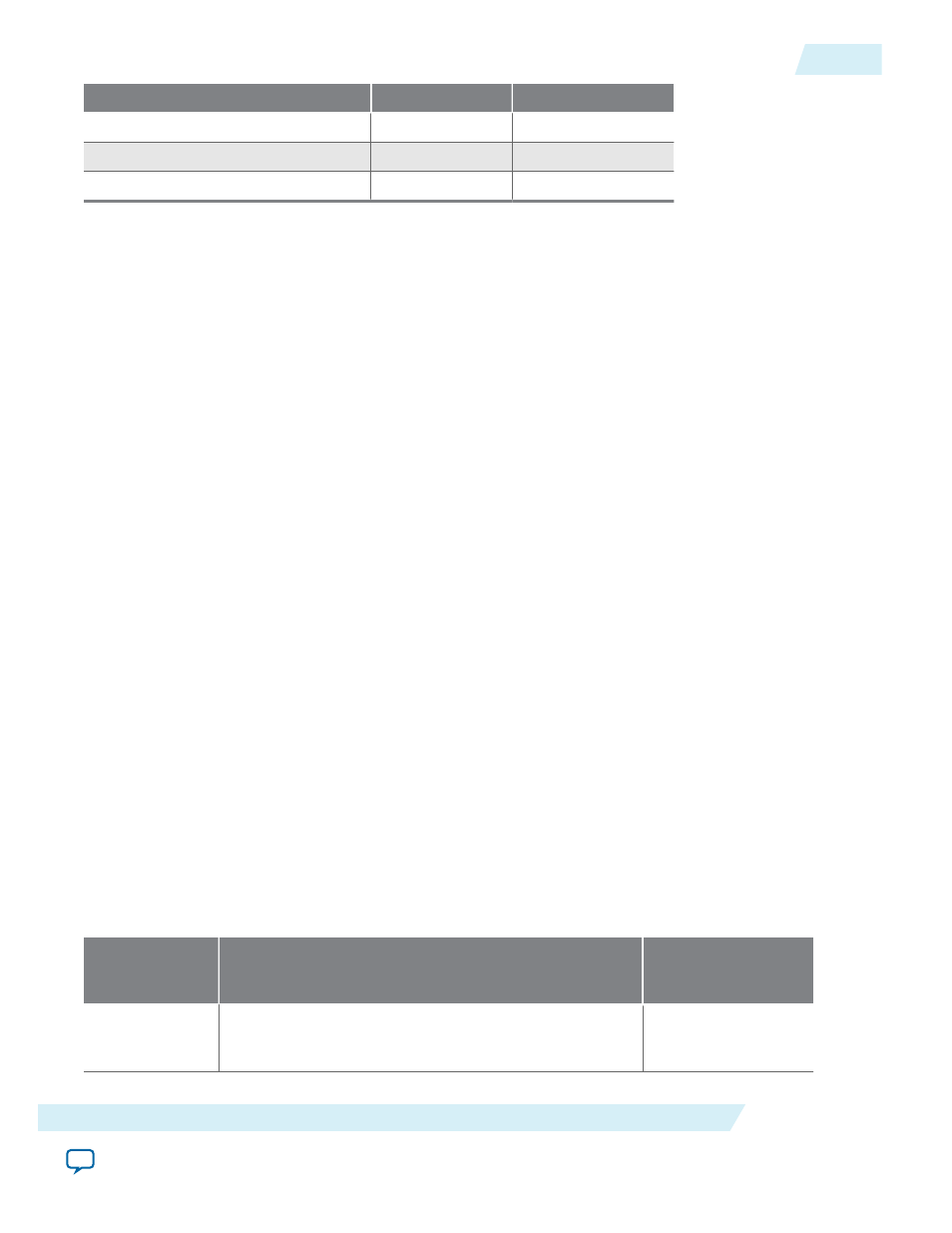

Parameter

Symbol

Value (ns)

Maximum clock-to-output time

t

CO_MAX

2.477

Maximum hold time after clock

t

H_MAX

–5.607

Maximum setup time before clock

t

SU_MAX

5.936

You must compile the design in the Quartus II software to obtain the I/O timing information for the

design. Although Altera device family datasheets contain generic I/O timing information for each device,

the Quartus II Compilation Report provides the most precise timing information for your specific design.

The timing values found in the compilation report can change, depending on fitting, pin location, and

other Quartus II logic settings. When you recompile the design in the Quartus II software, verify that the

I/O timing has not changed significantly.

The following examples illustrate the calculations from figures Maximum SDRAM Clock Lag and

Maximum Lead also using the values from the Timing Parameters and FPGA I/O Timing Parameters

table.

The SDRAM clock can lag the controller clock by the lesser of Read Lag or Write Lag:

Read Lag = t

OH

(SDRAM) – t

H_MAX

(FPGA)

= 2.5 ns – (–5.607 ns) = 8.107 ns

or

Write Lag = t

CLK

– t

CO_MAX

(FPGA) – t

DS

(SDRAM)

= 20 ns – 2.477 ns – 2 ns = 15.523 ns

The SDRAM clock can lead the controller clock by the lesser of Read Lead or Write Lead:

Read Lead = t

CO_MIN

(FPGA) – t

DH

(SDRAM)

= 2.399 ns – 1.0 ns = 1.399 ns

or

Write Lead = t

CLK

– t

HZ(3)

(SDRAM) – t

SU_MAX

(FPGA)

= 20 ns – 5.5 ns – 5.936 ns = 8.564 ns

Therefore, for this example you can shift the phase of the SDRAM clock from –8.107 ns to 1.399 ns

relative to the controller clock. Choosing a phase shift in the middle of this window results in the value (–

8.107 + 1.399)/2 = –3.35 ns.

Document Revision History

Table 2-5: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

V14.0

-Removed mention of SOPC Builder, updated to Qsys

Maintenance

Release

UG-01085

2014.24.07

Document Revision History

2-13

SDRAM Controller Core

Altera Corporation