Phase reconfig control register, Phase reconfig control register -7 – Altera Embedded Peripherals IP User Manual

Page 318

Phase Reconfig Control Register

Embedded software can control the dynamic phase reconfiguration via the

phase reconfig control

register.

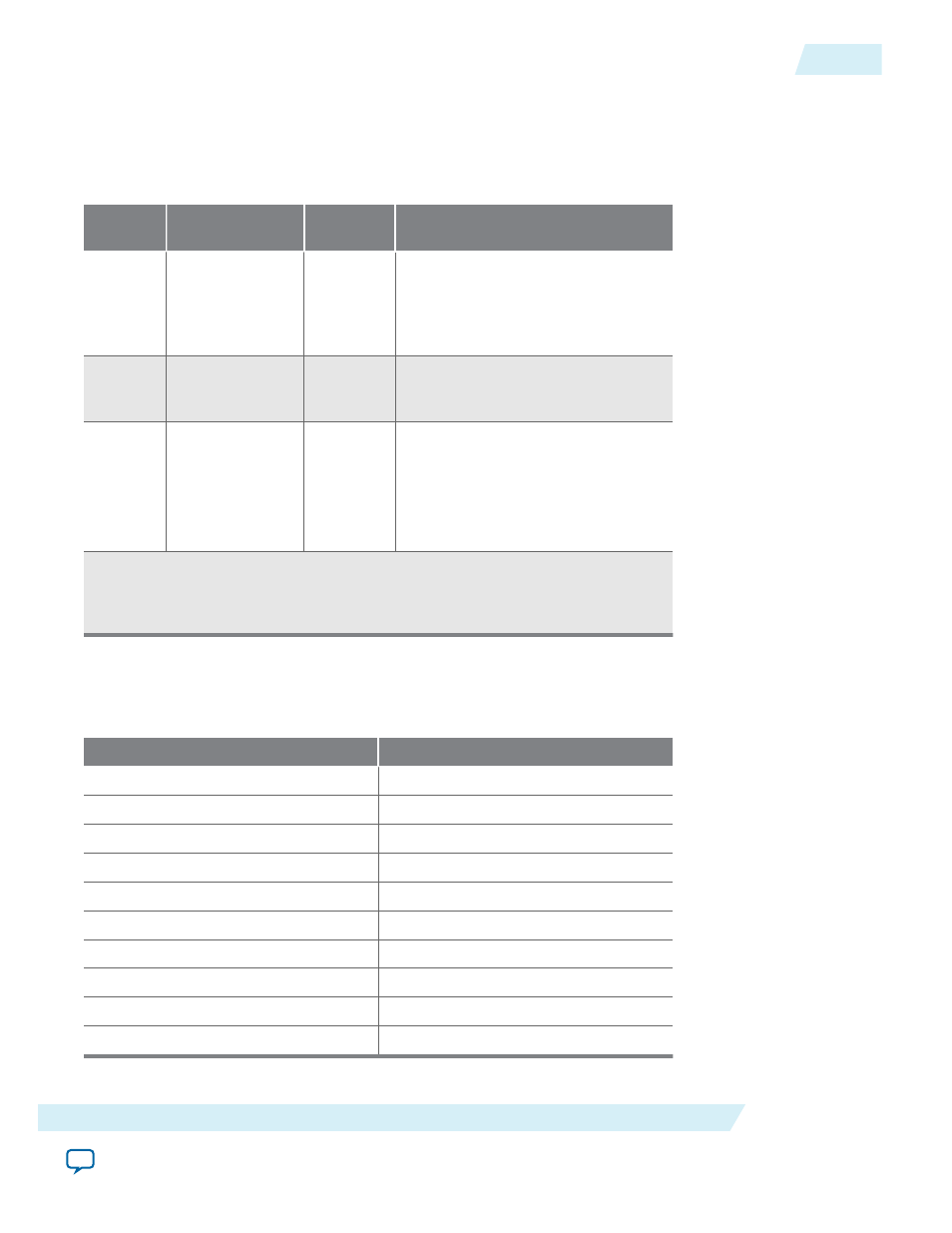

Table 32-5: Phase Reconfig Control Register Bits

Bit

Number

Bit Name

Value after

reset

Description

0:8

counter_number

—

A binary 9-bit representation of the

counter that needs to be reconfig‐

ured. Refer to the Counter_

Number Bits and Selection table

for the counter selection.

9:29

—

—

Reserved. Read values are

undefined. When writing, set

reserved bits to zero.

30:31

—

01: Step up phase of

counter_

number

10: Step down phase of

counter_

number

00 and 11: No operation

1. Phase step up or down when set to 1 (only applicable to the Avalon

ALTPLL core).

The table below lists the counter number and selection. For example, 100 000 000 selects counter C0 and

100 000 001 selects counter C1.

Table 32-6: Counter_Number Bits and Selection

Counter_Number [0:8]

Counter Selection

0 0000 0000

All output counters

0 0000 0001

M counter

> 0 0000 0001

Undefined

1 0000 0000

C0

1 0000 0001

C1

1 0000 0010

C2

...

...

1 0000 1000

C8

1 0000 1001

C9

> 1 0000 1001

Undefined

UG-01085

2014.24.07

Phase Reconfig Control Register

32-7

PLL Cores

Altera Corporation