Rtos considerations, Document revision history, Document revision history -23 – Altera Embedded Peripherals IP User Manual

Page 292

• Each component’s interrupt interface in your system should only be connected to one VIC instance

per processor.

• The number of shadow register sets for the processor must be greater than zero.

• RRS values must always be greater than zero and less than or equal to the number of shadow

register sets.

• RIL values must always be greater than zero and less than or equal to the maximum RIL.

• All RILs assigned to a register set must be sequential to avoid a higher priority interrupt overwriting

contents of a register set being used by a lower priority interrupt.

Note: The Nios II BSP Editor uses the term “overlap condition” to refer to nonsequential RIL

assignments.

• NMIs cannot share register sets with maskable interrupts.

• NMIs must have RILs set to a number equal to or greater than the highest RIL of any

maskable interrupt. When equal, the NMIs must have a lower logical interrupt port number

than any maskable interrupt.

• The vector table and funnel code section's memory device must connect to a data master and

an instruction master.

• NMIs must use funnels with preemption disabled.

• When global preemption is disabled, enabling preemption into a new register set or per-

register-set preemption might produce unpredictable results. Be sure that all interrupt

service routines (ISR) used by the register set support preemption.

• Enabling register set preemption for register sets with peripherals that don't support

preemption might result in unpredictable behavior.

RTOS Considerations

BSPs configured to use a real time operating system (RTOS) might have additional software linked into

the HAL interrupt funnel code using the

ALT_OS_INT_ENTER

and

ALT_OS_INT_EXIT

macros. The exact

nature and overhead of this code is RTOS-specific. Additional code adds to interrupt response and

recovery time. Refer to your RTOS documentation to determine if such code is necessary.

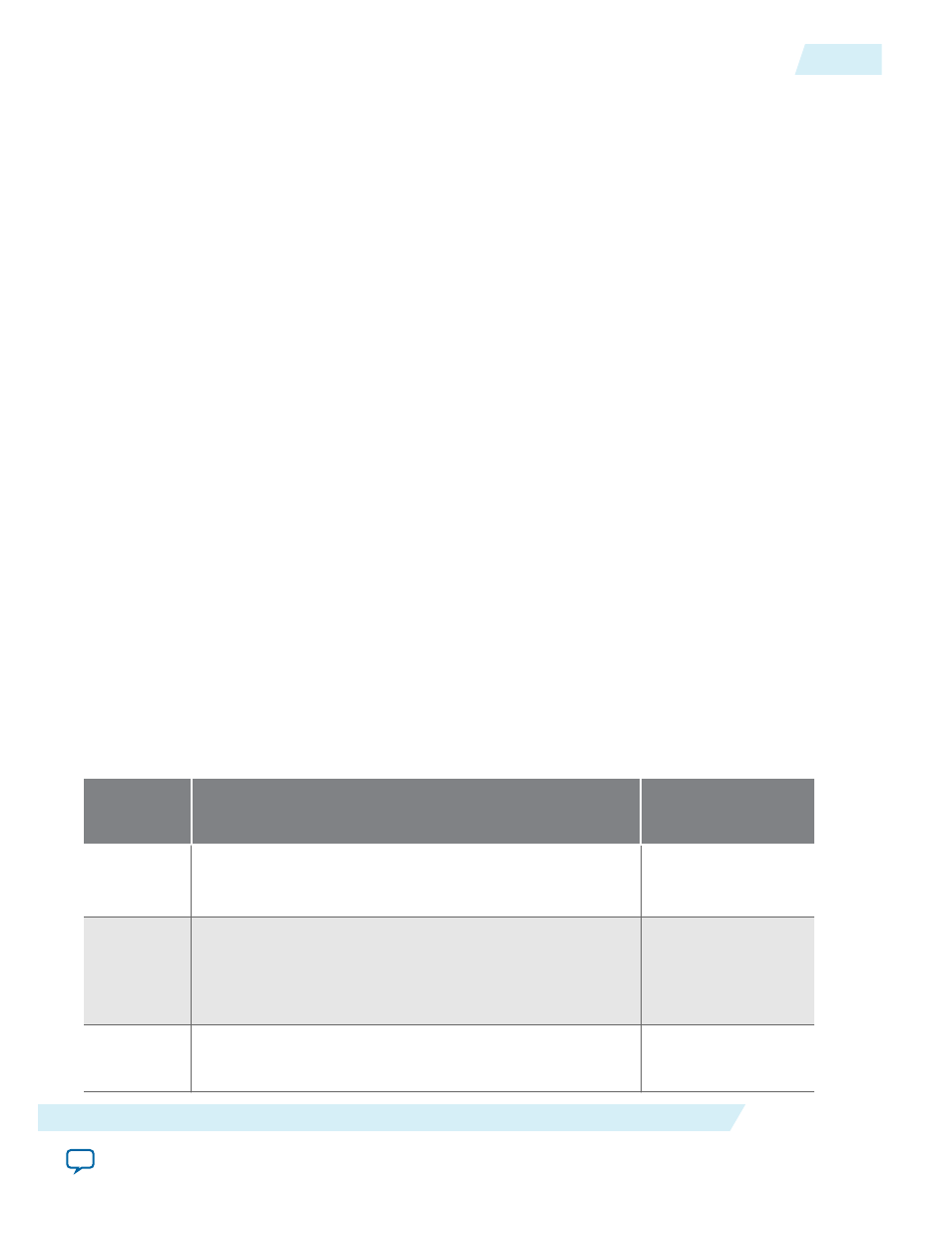

Document Revision History

Table 28-14: Revision History

Date and

Document

Version

Changes Made

Summary of Changes

December

2013

v13.1.0

Updated the

INT_ENABLE

register description.

—

December

2010

v10.1.0

Added a note to to state that the VIC does not support the

runtime stack checking feature in BSP setting.

Removed the “Device Support”, “Instantiating the Core in

SOPC Builder”, and “Referenced Documents” sections.

—

July 2010

v10.0.0

No change from previous release.

—

UG-01085

2014.24.07

RTOS Considerations

28-23

Vectored Interrupt Controller Core

Altera Corporation