Altera Embedded Peripherals IP User Manual

Page 239

length Register

The

length

register specifies the number of bytes to be transferred from the read port to the write port.

The

length

register is specified in bytes. For example, the value must be a multiple of 4 for word transfers,

and a multiple of 2 for halfword transfers.

The

length

register is decremented as each data value is written by the write master port. When

length

reaches 0 the

LEN

bit is set. The

length

register does not decrement below 0.

The length register width is determined at system generation time. It is at least wide enough to span any of

the slave ports mastered by the read or write master ports, and it can be made wider if necessary.

control Register

The control register is composed of individual bits that control the DMA’s internal operation. The control

register’s value can be read at any time. The control register bits determine which, if any, conditions of the

DMA transaction result in the end of a transaction and an interrupt request.

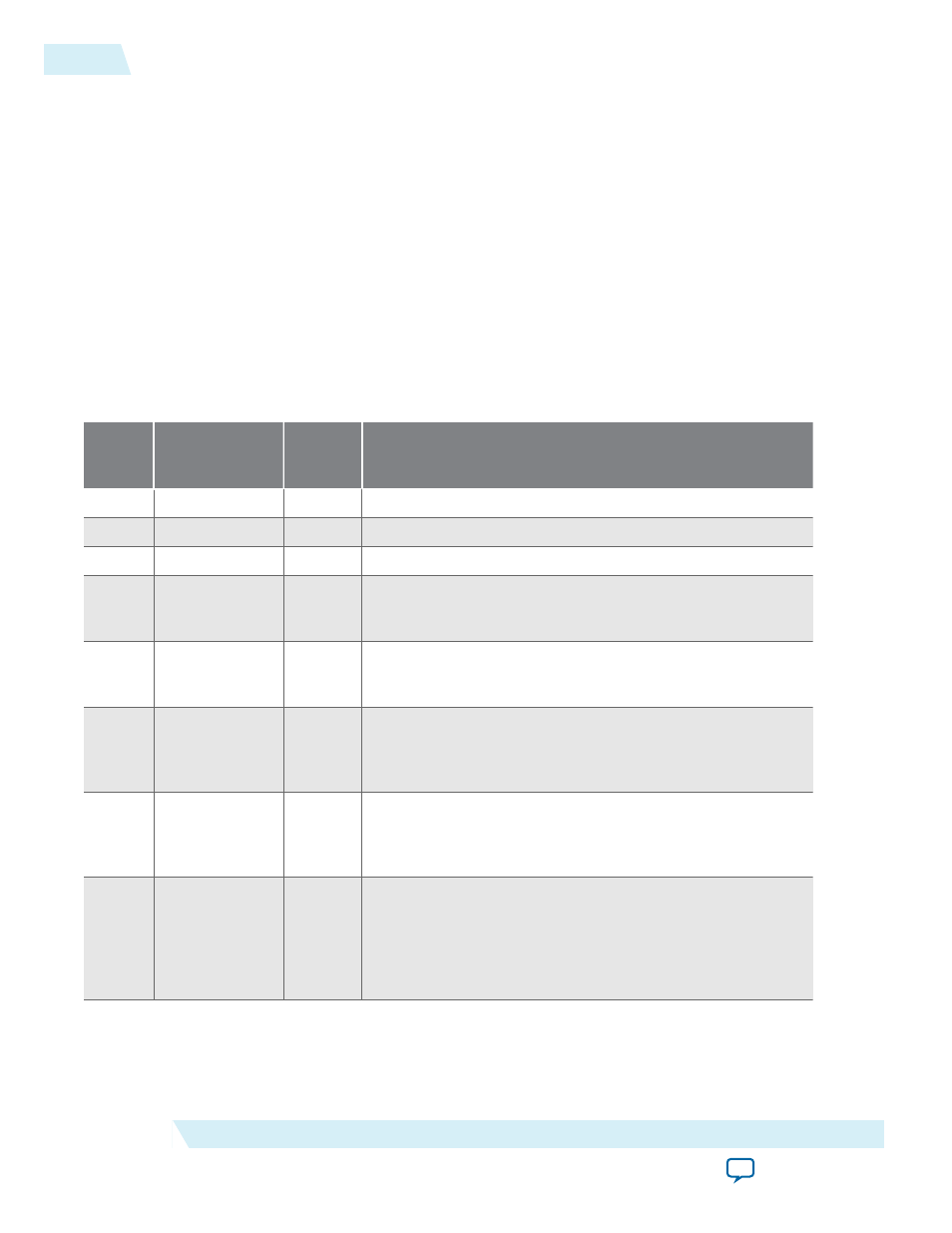

Table 23-5: Control Register Bits

Bit

Number

Bit Name

Read/

Write/

Clear

Description

0

BYTE

RW

Specifies byte transfers.

1

HW

RW

Specifies halfword (16-bit) transfers.

2

WORD

RW

Specifies word (32-bit) transfers.

3

GO

RW

Enables DMA transaction. When the

GO

bit is set to 0, the

DMA is prevented from executing transfers. When the

GO

bit

is set to 1 and the length register is non-zero, transfers occur.

4

I_EN

RW

Enables interrupt requests (IRQ). When the

I_EN

bit is 1, the

DMA controller generates an IRQ when the status register’s

DONE

bit is set to 1. IRQs are disabled when the

I_EN

bit is 0.

5

REEN

RW

Ends transaction on read-side end-of-packet. When the

REEN

bit is set to 1, a slave port with flow control on the read

side may end the DMA transaction by asserting its end-of-

packet signal.

6

WEEN

RW

Ends transaction on write-side end-of-packet. When the

WEEN

bit is set to 1, a slave port with flow control on the write

side may end the DMA transaction by asserting its end-of-

packet signal.

7

LEEN

RW

Ends transaction when the

length

register reaches zero.

When the

LEEN

bit is 1, the DMA transaction ends when the

length

register reaches 0. When this bit is 0,

length

reaching 0 does not cause a transaction to end. In this case,

the DMA transaction must be terminated by an end-of-

packet signal from either the read or write master port.

23-8

Register Map

UG-01085

2014.24.07

Altera Corporation

DMA Controller Core