Status register, Control register – Altera Embedded Peripherals IP User Manual

Page 229

Byte Lanes

0x18

N/A

1

0x1C

N/A

1

Status Register

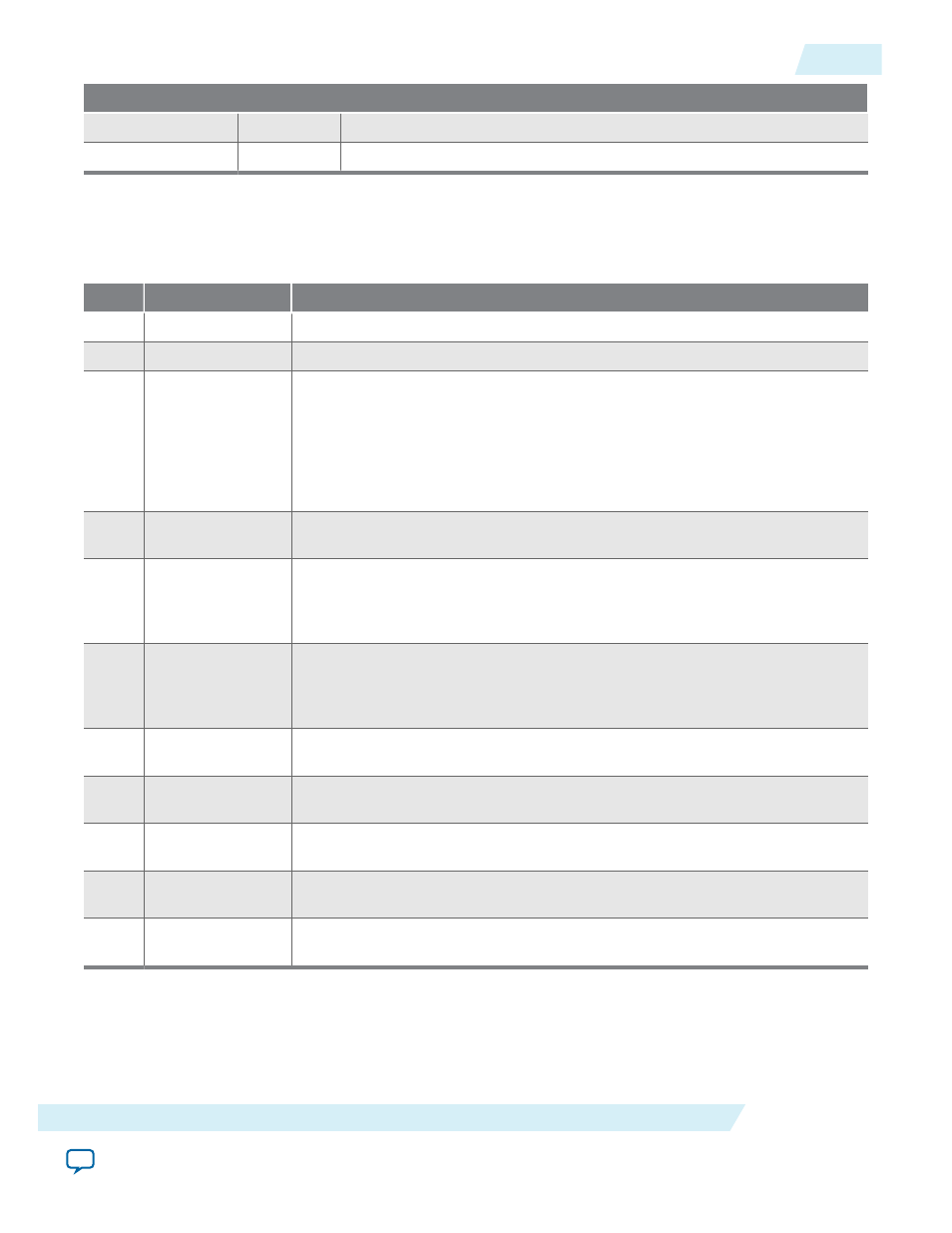

Table 22-5: Status Register Bit Definition

Bit

Name

Description

31:10

N/A

9

IRQ

Set when an interrupt condition occurs.

8

Stopped on Early

Termination

Set when the dispatcher is programmed to stop on early termination and when

the write master is performing a packet transfer and does not receive EOP

before the pre-determined amount of bytes are transferred which is set in the

descriptor length field. If you do not wish to use early termination you should

set the transfer length of the descriptor to 0xFFFFFFFF which will give you the

maximum packet based transfer possible (early termination is always enabled

for packet transfers).

7

Stopped on Error

Set when the dispatcher is programmed to stop errors and an error beat enters

the write master.

6

Resetting

Set when you write to the software reset register and the SGDMA is in the

middle of a reset cycle. This reset cycle is necessary to make sure there are no

transfers in flight on the fabric. When this bit de-asserts you may start using

the SGDMA again.

5

Stopped

Set when you either manually stop the SGDMA or you setup the dispatcher to

stop on errors or early termination and one of those conditions occurred. If

you manually stop the SGDMA this bit will be asserted after the master

completes any read or write operations that were already commencing.

4

Response Buffer

Full

Set when the response buffer is full.

3

Response Buffer

Empty

Set when the response buffer is empty.

2

Descriptor Buffer

Full

Set when either the read or write command buffers are full.

1

Descriptor Buffer

Empty

Set when both the read and write command buffers are empty.

0

Busy

Set when the dispatcher still has commands buffered or one of the masters is

still transferring data.

Control Register

UG-01085

2014.24.07

Status Register

22-13

Altera Modular Scatter-Gather DMA

Altera Corporation