Register map of msgdma, Register map of msgdma -12 – Altera Embedded Peripherals IP User Manual

Page 228

Bit

Sub-Field Name

Definition

12

End on EOP

End on end of packet allows the write

master to continuously transfer data

during ST->MM transfers without

knowing how much data is arriving

ahead of time.

This bit is commonly set for packet-

based traffic such as Ethernet.

11

Park Writes

When set, the dispatcher continues to

reissue the same descriptor to the

write master when no other descrip‐

tors are buffered.

10

Park Reads

When set, the dispatcher continues to

reissue the same descriptor to the

read master when no other descrip‐

tors are buffered. This is commonly

used for video frame buffering.

9

Generate EOP

Used to emit an end of packet on last

beat of a MM->ST transfer

8

Generate SOP

Used to emit a start of packet on the

first beat of a MM->ST transfer

7:0

Transmit Channel

Used to emit a channel number

during MM->ST transfers

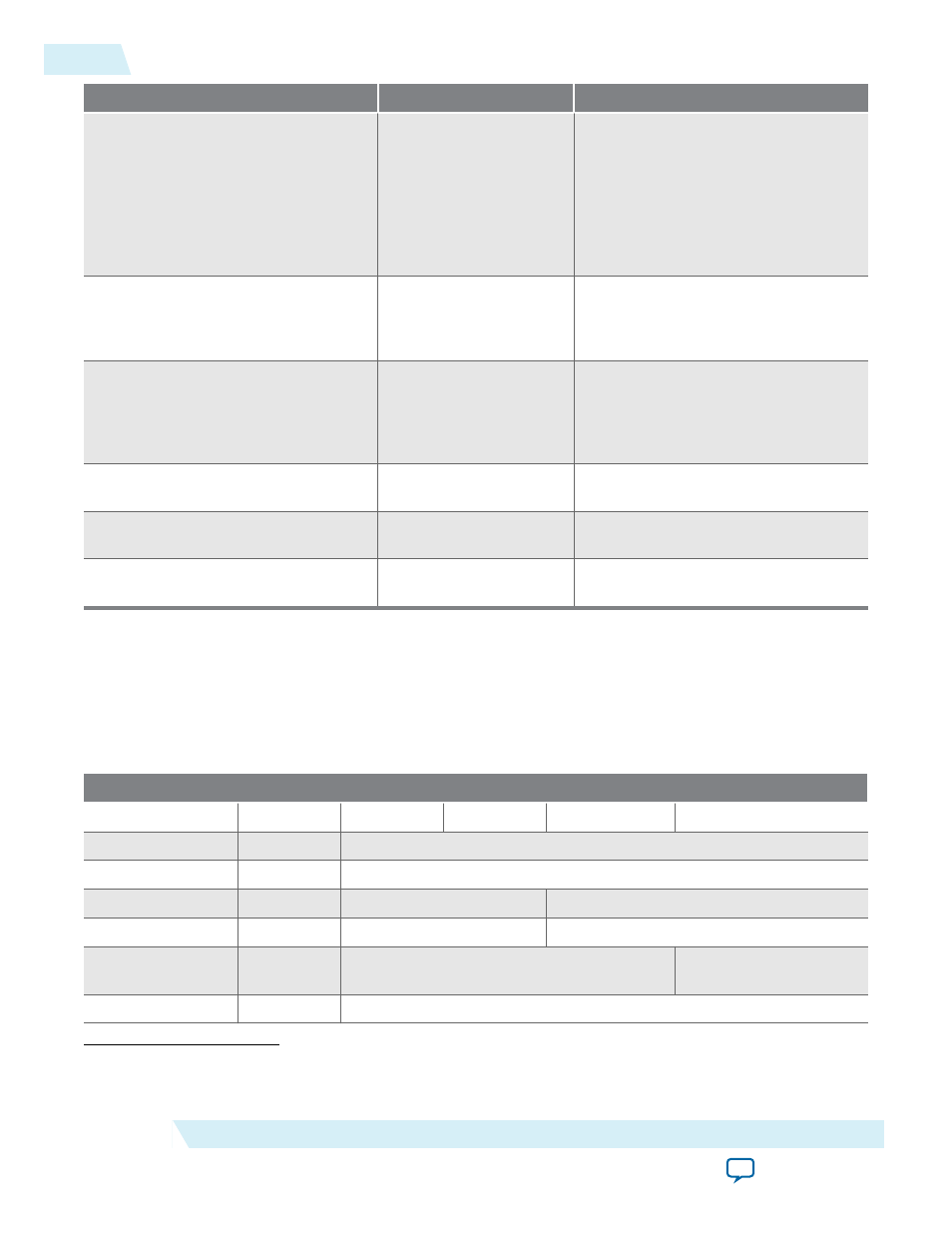

Register Map of mSGDMA

The following table illustrates the Altera mSGDMA registers map being observed by host processor from

its Avalon-MM CSR interfaces.

Table 22-4: CSR Registers Map

Byte Lanes

Offset

Attribute

3

2

1

0

0x0

Read/Clear

Status

0x4

Read/Write Control

0x8

Read

Write Fill Level[15:0]

Read Fill Level[15:0]

0xC

Read

(1)

Response Fill Level[15:0]

0x10

Read

Write Sequence Number[15:0]

(2)

Read Sequence

Number[15:0]

2

0x14

N/A

1

(1)

Writing to reserved bits will have no impact on the hardware, reading will return unknown data.

(2)

Sequence numbers will only be present when dispatcher enhanced features are enabled.

22-12

Register Map of mSGDMA

UG-01085

2014.24.07

Altera Corporation

Altera Modular Scatter-Gather DMA