Pci interrupt, Configuration, Pci interrupt -10 – Altera Embedded Peripherals IP User Manual

Page 144: Configuration -10

• PMW—Posted memory write.

• DRR—Delayed read request.

• DWR—Delayed write request. DWRs are I/O or configuration write operation requests. The PCI-

Avalon bridge does not handle DWRs as delayed writes.

• As a PCI master, I/O or configuration writes are generated from posted Avalon-MM writes. If

required to verify completion, you must issue a subsequent read request to the same target.

• As a PCI target, configuration writes are the only requests accepted, which are never delayed. These

requests are handled directly by the PCI core.

• DRC—Delayed read completion.

• DWC—Delayed write completion. These are never passed through to the core in either direction.

Incoming configuration writes are never delayed. Delayed write completion status is not passed back at

all.

Every single transaction that is initiated, locks the core until it is completed. Only then can a new

transaction be accepted.

PCI Interrupt

When Avalon-MM asserts the

IRQ

signal, an interrupt on the PCI bus occurs. The Avalon-MM

IRQ

input

causes a bit to be set in the PCI interrupt status register.

Configuration

The table below describes the parameters that can be configured in SOPC Builder for the PCI Lite core.

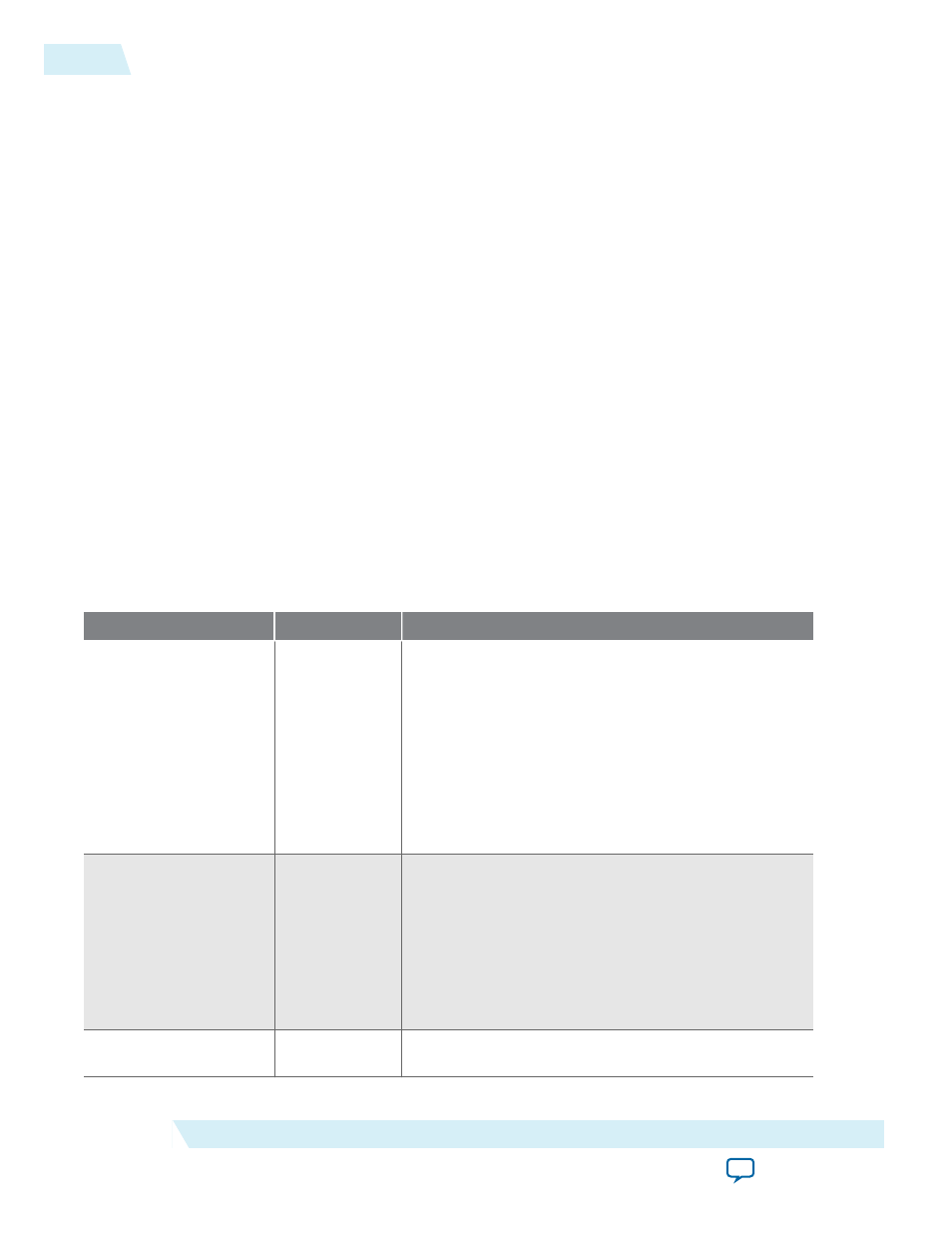

Table 14-9: Parameters for PCI Lite Core

Parameters

Legal Values

Description

Enable Master/Target

Mode

On or Off

Turning this option On enables Master/Target mode.

This option enables allows Avalon-MM master devices

to access PCI target devices via the PCI bus master

interface, and PCI bus master devices to access

Avalon-MM slave devices via the PCI bus target

interface.

Turning this option Off means you have selected

Target Only mode, which allows PCI bus mastering

devices to access Avalon-MM slave devices via the PCI

bus target interface.

Enable Host Bridge

Mode

On or Off

Turning this option On enables this mode.

In addition to the same features provided by the PCI

Master/Target mode, Host Bridge Mode provides host

bridge functionality including hardwiring the master

enable bit to 1 in the PCI command register and

allowing self-configuration. This value can only be set

if the Enable Master/Target Mode option is turned

On.

Number of Address

Pages

2, 4, 8, or 16

The number of translation/pages supported by the

device for Avalon to PCI address translation.

14-10

PCI Interrupt

UG-01085

2014.24.07

Altera Corporation

PCI Lite Core