Data input and output, Edge capture, Irq generation – Altera Embedded Peripherals IP User Manual

Page 124: Data input and output -2, Edge capture -2, Irq generation -2, Figure 12-1: system using multiple pio cores

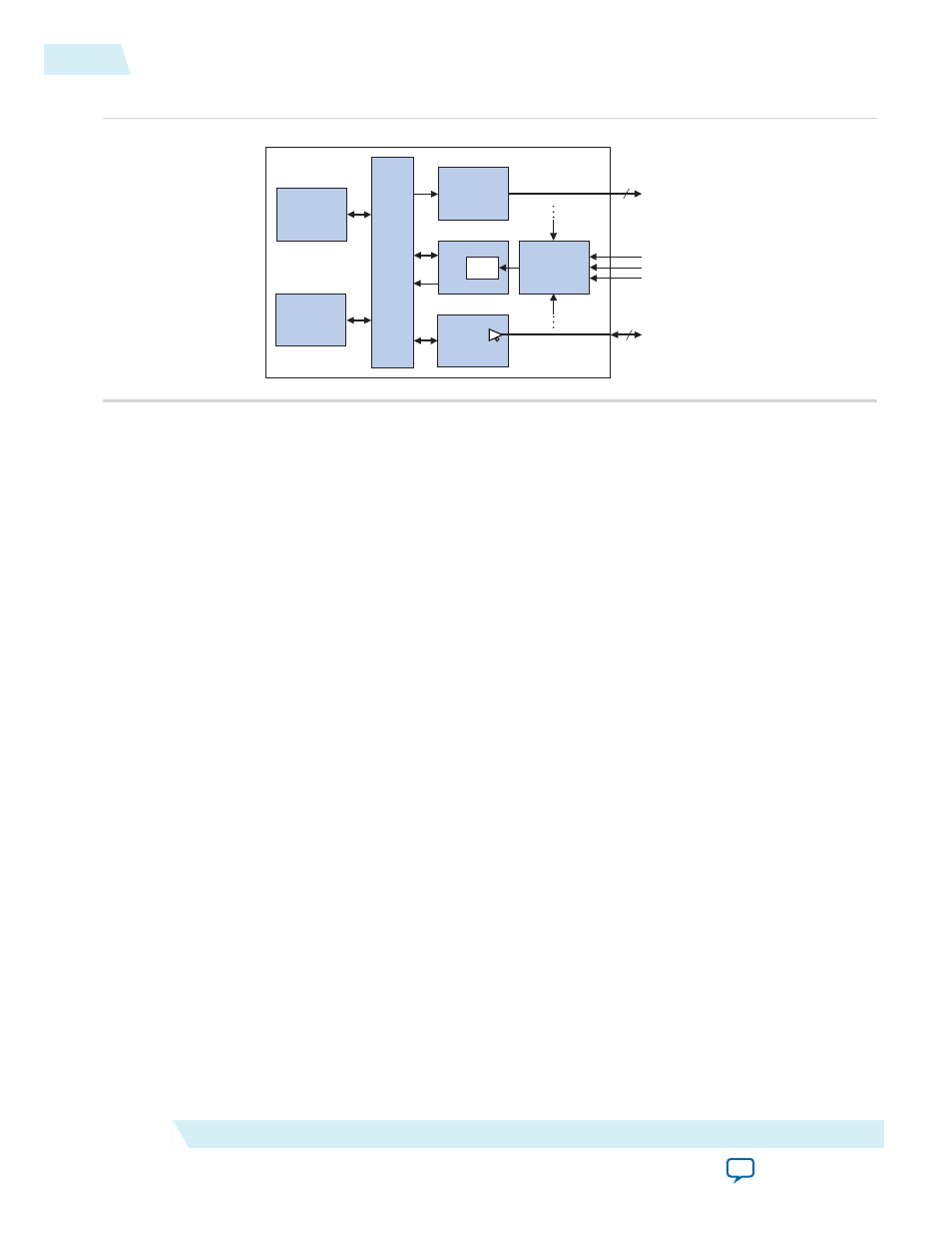

Figure 12-1: System Using Multiple PIO Cores

System Interconnect

Fab

ric

CPU

PIO core

(output only)

Program

and Data

Memory

PIO

core

(bidirectional)

IRQ

LEDs

Edge

Capture

PIO

core

(input

only)

Reset

request

logic

Altera FPGA

4

11

LCD

display

When integrated into an Qsys-generated system, the PIO core has two user-visible features:

• A memory-mapped register space with four registers:

data

,

direction

,

interruptmask

, and

edgecapture

• 1 to 32 I/O ports

The I/O ports can be connected to logic inside the FPGA, or to device pins that connect to off-chip

devices. The registers provide an interface to the I/O ports via the Avalon-MM interface. See Register

Map for the PIO Core table for a description of the registers.

Data Input and Output

The PIO core I/O ports can connect to either on-chip or off-chip logic. The core can be configured with

inputs only, outputs only, or both inputs and outputs. If the core is used to control bidirectional I/O pins

on the device, the core provides a bidirectional mode with tristate control.

The hardware logic is separate for reading and writing the data register. Reading the data register returns

the value present on the input ports (if present). Writing data affects the value driven to the output ports

(if present). These ports are independent; reading the data register does not return previously-written

data.

Edge Capture

The PIO core can be configured to capture edges on its input ports. It can capture low-to-high transitions,

high-to-low transitions, or both. Whenever an input detects an edge, the condition is indicated in the

edgecapture

register. The types of edges detected is specified at system generation time, and cannot be

changed via the registers.

IRQ Generation

The PIO core can be configured to generate an IRQ on certain input conditions. The IRQ conditions can

be either:

12-2

Data Input and Output

UG-01085

2014.24.07

Altera Corporation

PIO Core