Width, Direction, Output port reset value – Altera Embedded Peripherals IP User Manual

Page 126: Output register, Input options, Input options -4

Width

The width of the I/O ports can be set to any integer value between 1 and 32.

Direction

You can set the port direction to one of the options shown below.

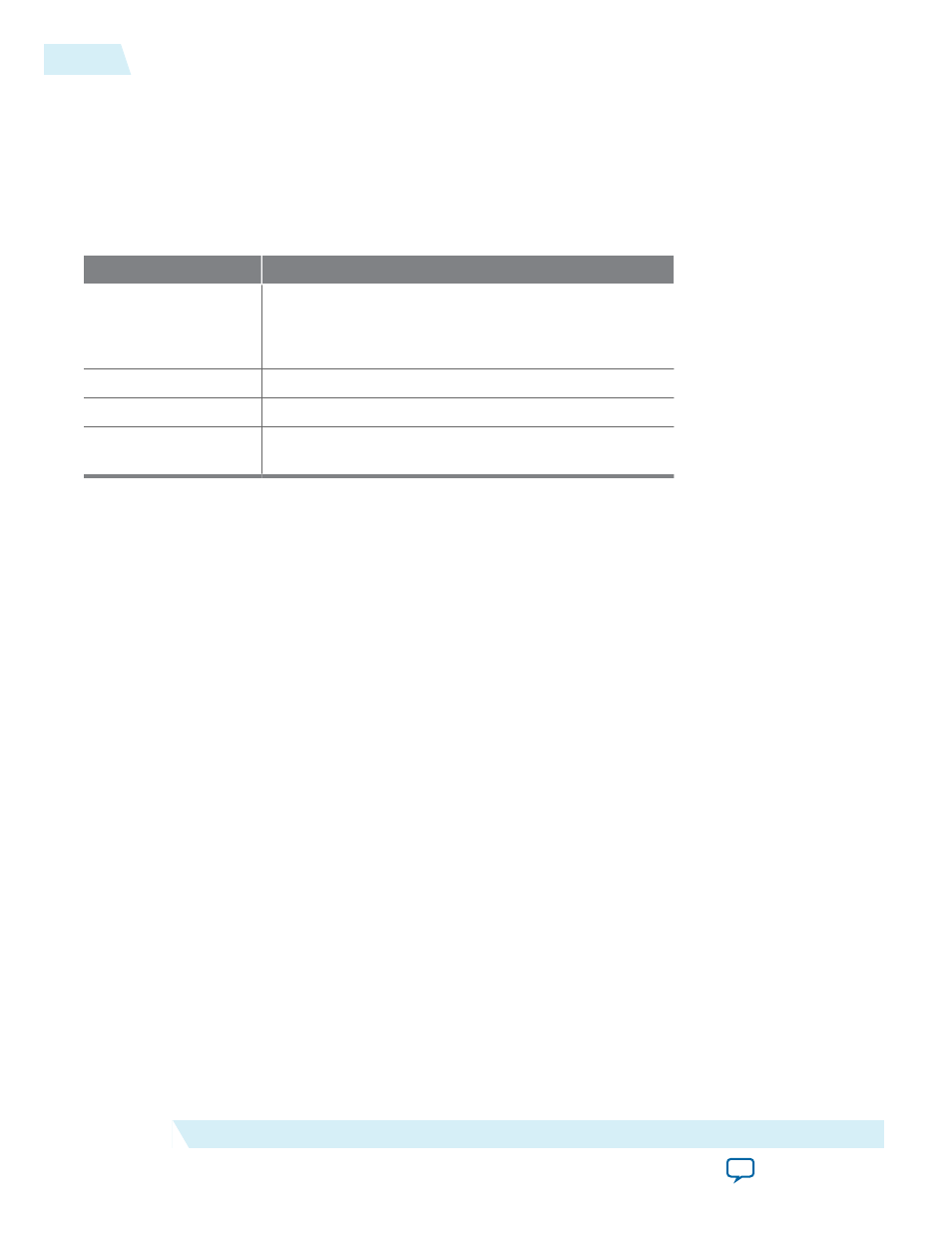

Table 12-1: Direction Settings

Setting

Description

Bidirectional

(tristate) ports

In this mode, each PIO bit shares one device pin for

driving and capturing data. The direction of each pin is

individually selectable. To tristate an FPGA I/O pin, set

the direction to input.

Input ports only

In this mode the PIO ports can capture input only.

Output ports only

In this mode the PIO ports can drive output only.

Both input and

output ports

In this mode, the input and output ports buses are

separate, unidirectional buses of n bits wide.

Output Port Reset Value

You can specify the reset value of the output ports. The range of legal values depends on the port width.

Output Register

The option Enable individual bit set/clear output register allows you to set or clear individual bits of the

output port. When this option is turned on, two additional registers—

outset

and

outclear

—are

implemented. You can use these registers to specify the output bit to set and clear.

Input Options

The Input Options page allows you to specify edge-capture and IRQ generation settings. The Input

Options page is not available when Output ports only is selected on the Basic Settings page.

12-4

Width

UG-01085

2014.24.07

Altera Corporation

PIO Core