Resource usage and performance, Resource usage and performance -2 – Altera Embedded Peripherals IP User Manual

Page 193

Figure 21-1: SG-DMA Controller Core with Streaming Peripheral and External Memory

Altera FPGA

S OPC Builde r Syste m

S

Sc a tter Ga ther DMA Control ler Core

Nios II

Proc e s s o r

Rd

SN K

De s c ripto r

Proce s sor

Blo c k

DDR2

S DRAM

Me mo ry

Co ntrol ler

M

Rd

M

DMA Write

Block

M

Wr

M

Wr

M

Co ntrol

&

S tatus

Registe rs

S yst e m Interco nne ct Fa bric

Me mo ry

De sc riptor

Ta ble

S

Ava lon-MM Sla ve P ort

S NK

Ava lon-S T S ink P ort

M

Avalon-MM Mas ter P ort

St ream ing

Com ponent

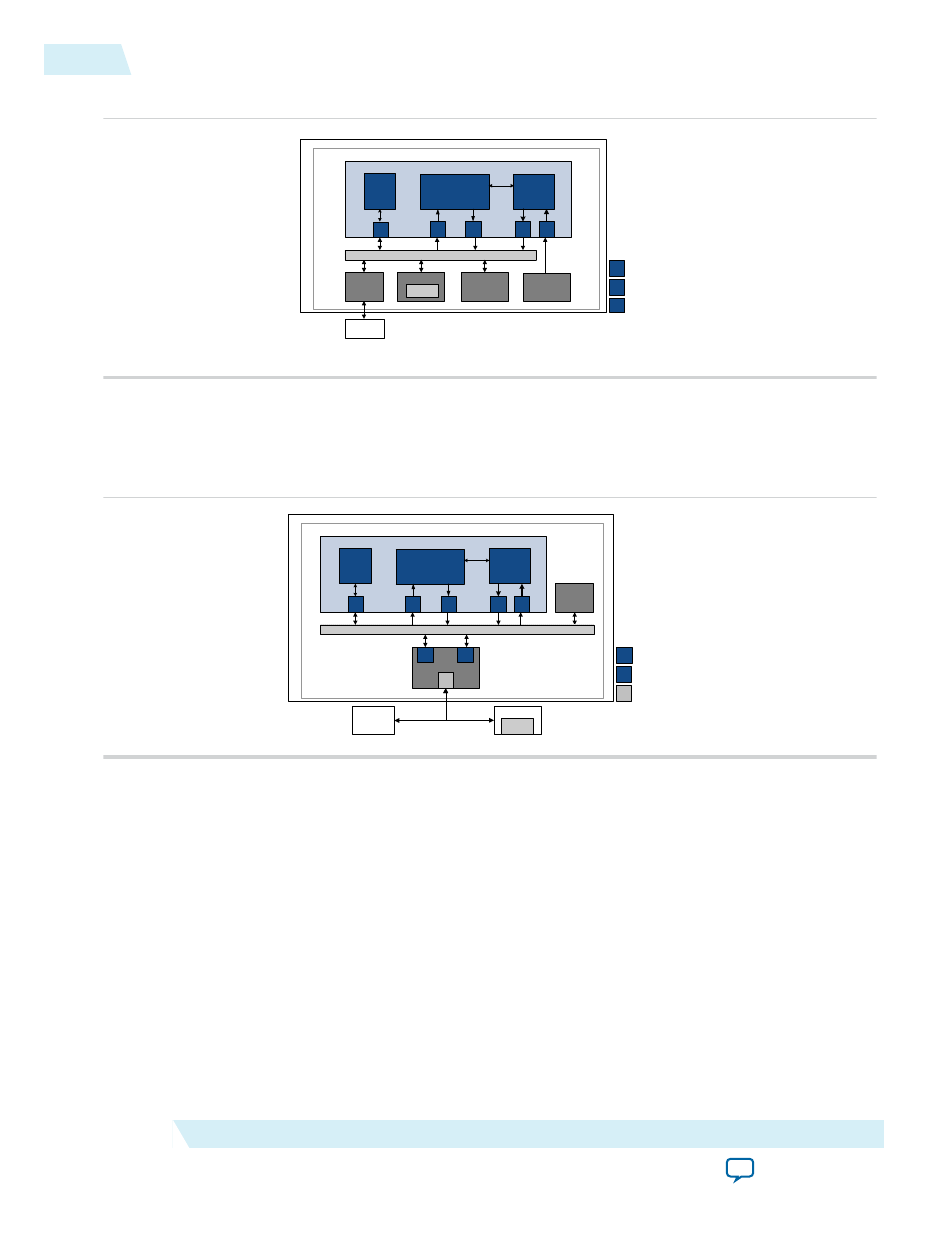

The figure below shows a different use of the SG-DMA controller core, where the core transfers data

between an internal and external memory. The host processor and memory are connected to a system

bus, typically either a PCI Express or Serial RapidIO

™

.

Figure 21-2: SG-DMA Controller Core with Internal and External Memory

P roc e ss or

Bus

Altera FP GA

S OP C Builde r Syste m

S

Host P roc e ss or

Inte rnal

Memo ry

M

M

S ys tem Inte rconnec t Fa bric

S

Rd

M

De s c ripto r

Pro c e s sor

Block

Rd

M

DMA Re ad/

Write

Blo c k

Wr

M

Wr

M

Con trol

&

Stat us

Re g iste rs

S ca tte r Ga the r DMA Controlle r Core

Avalo n-MM Bridge

M

S

IOB

Main Me mo ry

De sc riptor

Table

S

Ava lon-MM S la ve Por t

M

Ava lon-MM Master P ort

IOB

IO Bre a kout

Comparison of SG-DMA Controller Core and DMA Controller Core

The SG-DMA controller core provides a significant performance enhancement over the previously

available DMA controller core, which could only queue one transfer at a time. Using the DMA Controller

core, a CPU had to wait for the transfer to complete before writing a new descriptor to the DMA slave

port. Transfers to non-contiguous memory could not be linked; consequently, the CPU overhead was

substantial for small transfers, degrading overall system performance. In contrast, the SG-DMA controller

core reads a series of descriptors from memory that describe the required transactions and performs all of

the transfers without additional intervention from the CPU.

Resource Usage and Performance

Resource utilization for the core is 600–1400 logic elements, depending upon the width of the datapath,

the parameterization of the core, the device family, and the type of data transfer. The table below provides

21-2

Comparison of SG-DMA Controller Core and DMA Controller Core

UG-01085

2014.24.07

Altera Corporation

Scatter-Gather DMA Controller Core