Interrupt behavior, Document revision history, Interrupt behavior -8 – Altera Embedded Peripherals IP User Manual

Page 256: Document revision history -8

period_n Registers

The

period_

n registers together store the timeout period value. The internal counter is loaded with the

value stored in these registers whenever one of the following occurs:

• A write operation to one of the

period_

n register

• The internal counter reaches 0

The timer's actual period is one cycle greater than the value stored in the

period_

n registers because

the counter assumes the value zero for one clock cycle.

Writing to one of the

period_

n registers stops the internal counter, except when the hardware is

configured with Start/Stop control bits off. If Start/Stop control bits is off, writing either register

does not stop the counter. When the hardware is configured with Writeable period disabled, writing

to one of the

period_

n registers causes the counter to reset to the fixed Timeout Period specified at

system generation time.

snap_n Registers

A master peripheral may request a coherent snapshot of the current internal counter by performing a

write operation (write-data ignored) to one of the

snap_

n registers. When a write occurs, the value of the

counter is copied to

snap_

n registers. The snapshot occurs whether or not the counter is running.

Requesting a snapshot does not change the internal counter's operation.

Interrupt Behavior

The interval timer core generates an IRQ whenever the internal counter reaches zero and the

ITO

bit of

the

control

register is set to 1. Acknowledge the IRQ in one of two ways:

• Clear the

TO

bit of the

status

register

• Disable interrupts by clearing the

ITO

bit of the

control

register

Failure to acknowledge the IRQ produces an undefined result.

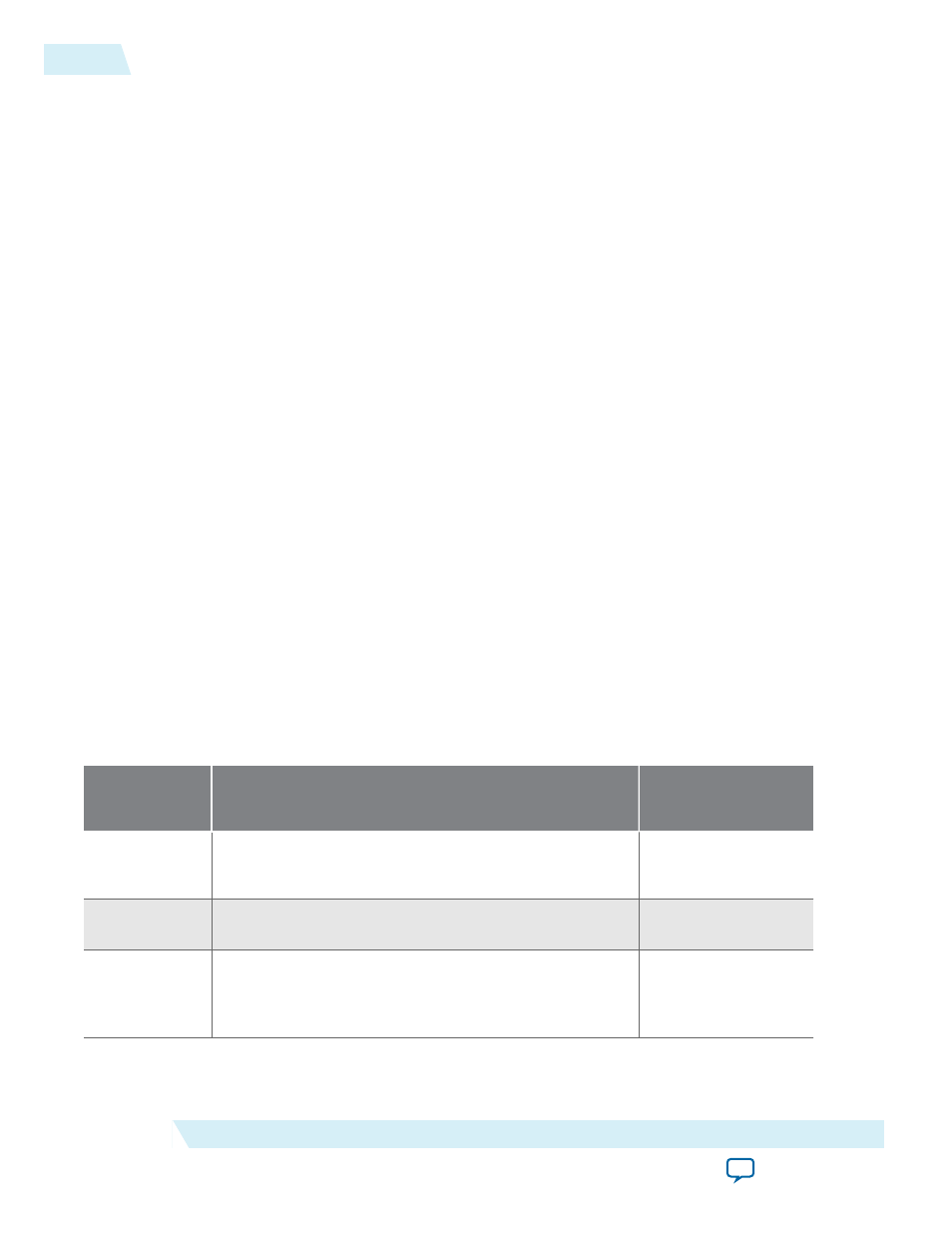

Document Revision History

Table 25-7: Document Revision History

Date and

Document

Version

Changes Made

Summary of Changes

July 2014

v14.0.0

-Removed mention of SOPC Builder, updated to Qsys

Maintenance

Release

December

2013 v13.1.0

Updated the reset pulse description in the Configuring the

Timer as a Watchdog Timer section.

—

December

2010

v10.1.0

Removed the “Device Support”, “Instantiating the Core in

SOPC Builder”, and “Referenced Documents” sections.

—

25-8

Interrupt Behavior

UG-01085

2014.24.07

Altera Corporation

Interval Timer Core