Altera Embedded Peripherals IP User Manual

Page 277

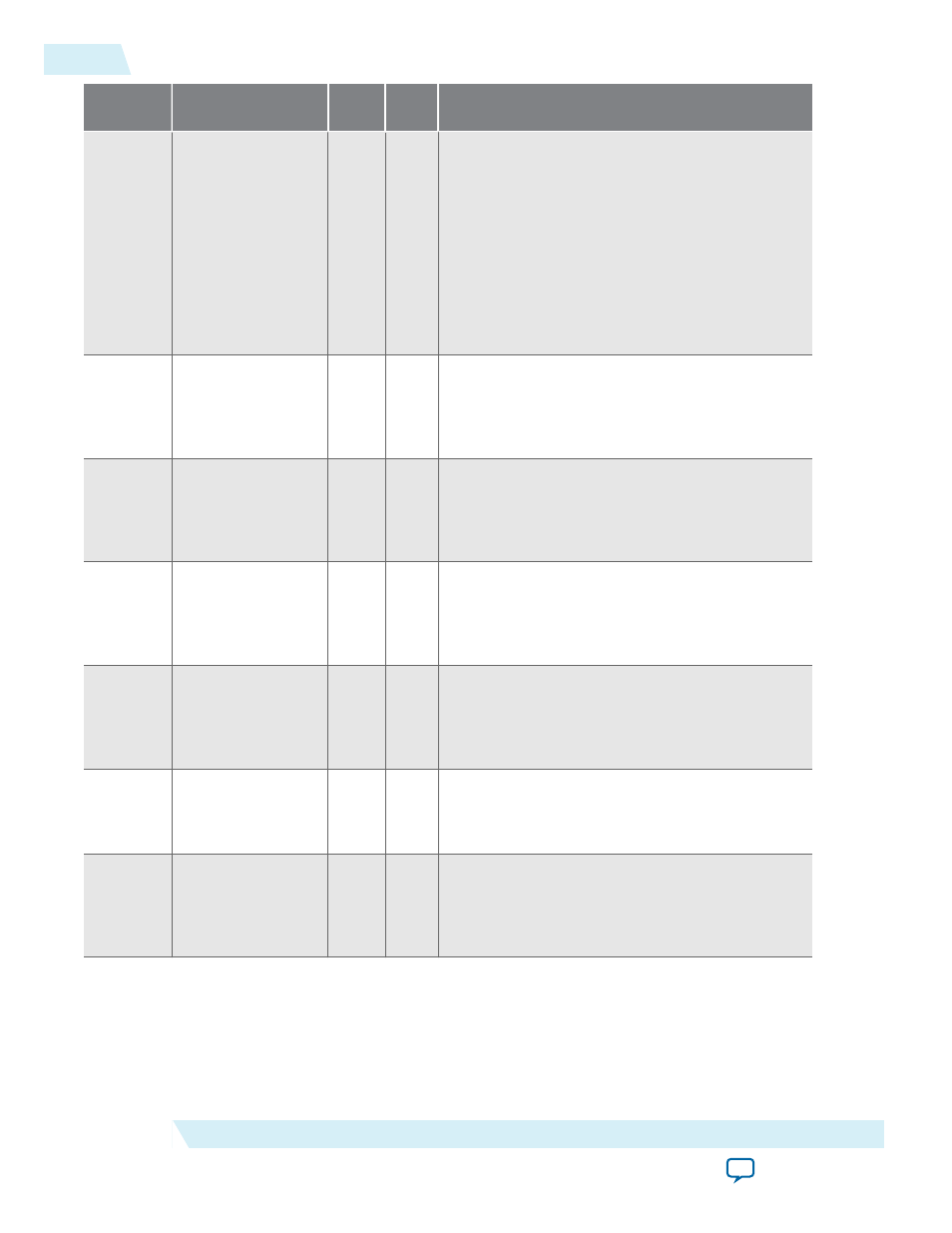

Offset

Register Name

Access Reset

Value

Description

36

INT_RAW_STATUS

R

0

The interrupt raw status register.

INT_RAW_

STATUS

shows the unmasked state of the

interrupt inputs.

If an interrupt does not exist, reading the

corresponding

INT_RAW_STATUS

bit always

returns 0, and writing is ignored.

A set bit indicates an interrupt is asserted at the

interface of the VIC. The interrupt is asserted to

the processor only when the corresponding bit in

the interrupt enable register is set.

37

SW_INTERRUPT

R/W

0

The software interrupt register.

SW_INTERRUPT

drives the software interrupts. Each interrupt is

ORed with its external hardware interrupt and

then enabled with

INT_ENABLE

. Refer to the

Interrupt Request Block for details.

38

SW_INTERRUPT_SET

W

0

The software interrupt set register. Writing a 1 to

a bit in

SW_INTERRUPT_SET

sets the

corresponding bit in

SW_INTERRUPT

. Writing a 0

to a bit has no effect. Reading from this register

39

SW_INTERRUPT_CLR

W

0

The software interrupt clear register. Writing a 1

to a bit in

SW_INTERRUPT_CLR

clears the

corresponding bit in

SW_INTERRUPT

. Writing a 0

to a bit has no effect. Reading from this register

40

VIC_CONFIG

R/W

0

The VIC configuration register.

VIC_CONFIG

allows software to configure settings that apply to

the entire VIC. Refer to the VIC_CONFIG

Register Map table for the

VIC_CONFIG

register

map.

41

VIC_STATUS

R

0

The VIC status register.

VIC_STATUS

shows the

current status of the VIC. Refer to the VIC_

STATUS Register Map table for the

VIC_STATUS

register map.

42

VEC_TBL_BASE

R/W

0

The vector table base register.

VEC_TBL_BASE

holds the base address of the vector table in the

processor’s memory space. Because the table

must be aligned on a 4-byte boundary, bits 1:0

must always be 0.

28-8

Register Maps

UG-01085

2014.24.07

Altera Corporation

Vectored Interrupt Controller Core