Functional description, External interfaces, Functional description -3 – Altera Embedded Peripherals IP User Manual

Page 272: External interfaces -3

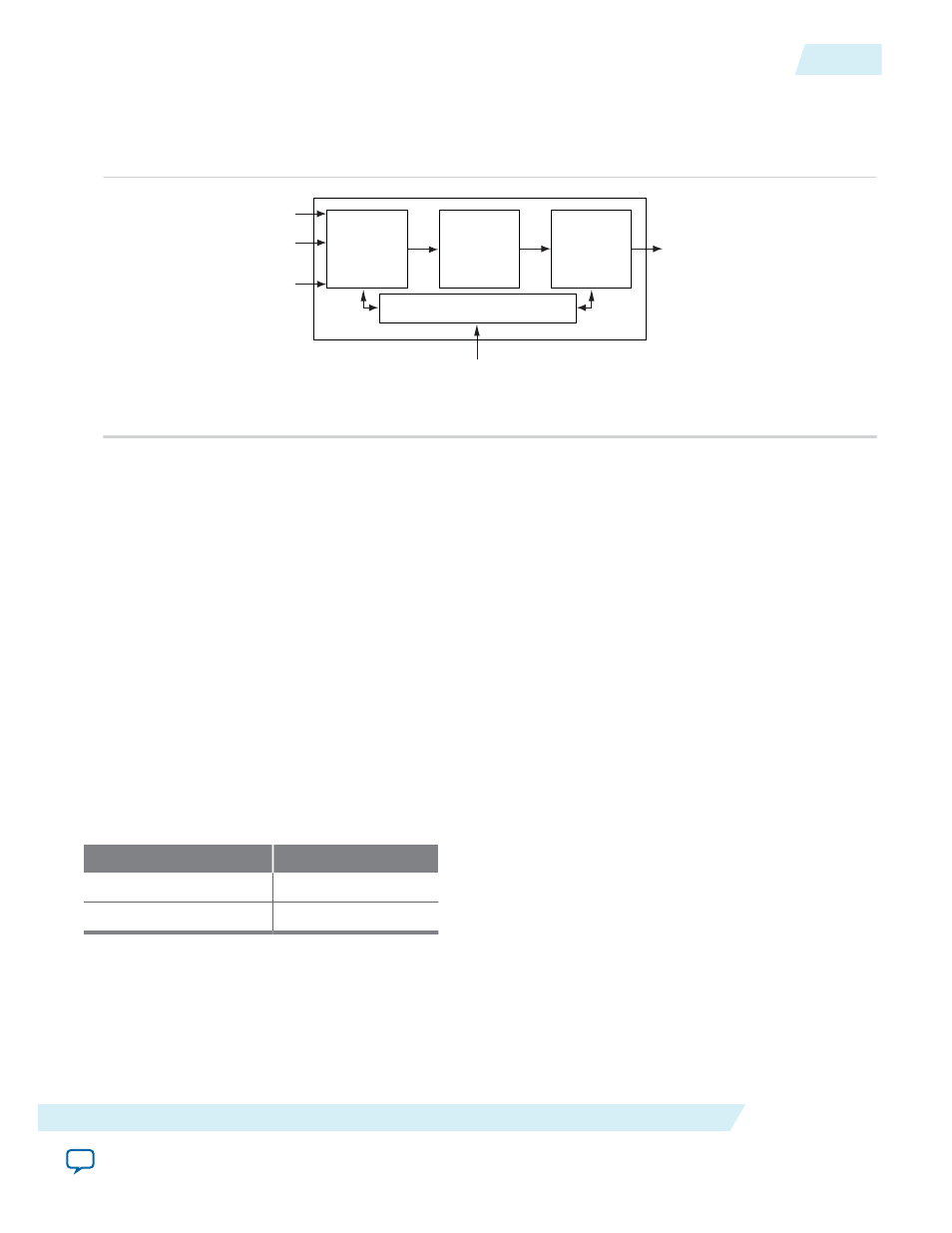

Functional Description

Figure 28-2: VIC Block Diagram

Control Status Regis

ters

csr_access

(Avalon-MM slave

from processor)

Interrupt

Request

Block

interrupt_controller_in

(optional Avalon-ST

VIC daisy chain input)

Vector

Generation

Block

Priority

Processing

Block

interrupt_controller_out

(Avalon-ST to processor or

to interrupt_controller_in

of another VIC)

clk

(clock)

irq_input

(external interrupt input)

External Interfaces

The following sections describe the external interfaces for the VIC core.

clk

clk

is a system clock interface. This interface connects to your system’s main clock source. The interface’s

signals are

clk

and

reset_n

.

irq_input

irq_input

comprises up to 32 single-bit, level-sensitive Avalon interrupt receiver interfaces. These

interfaces connect to interrupt sources. There is one

irq

signal for each interface.

interrupt_controller_out

interrupt_controller_out

is an Avalon-ST output interface, as defined in the VIC Avalon-ST

Interface Fields, configured with a ready latency of 0 cycles. This interface connects to your processor or

to the

interrupt_controller_in

interface of another VIC. The interface’s signals are

valid

and

data

.

Table 28-1: interrupt_controller_out and interrupt_controller_in Parameters

Parameter

Value

Symbol width

45 bits

Ready latency

0 cycles

interrupt_controller_in

interrupt_controller_in

is an optional Avalon-ST input interface, as defined in VIC Avalon-ST

Interface Fields, configured with a ready latency of 0 cycles. Include this interface in the second, third,

etc, VIC components of a daisy-chained multiple VIC system. This interface connects to the

interrupt_controller_out

interface of the immediately-preceding VIC in the chain. The interface’s

signals are

valid

and

data

.

UG-01085

2014.24.07

Functional Description

28-3

Vectored Interrupt Controller Core

Altera Corporation