Rockwell Automation 21G PowerFlex 750-Series AC Drives Programming Manual User Manual

Page 279

Rockwell Automation Publication 750-PM001J-EN-P - October 2014

279

Embedded Feature and Option Module Parameters

Chapter 5

Univ

ersal F

ee

dback

Feedback 0

16

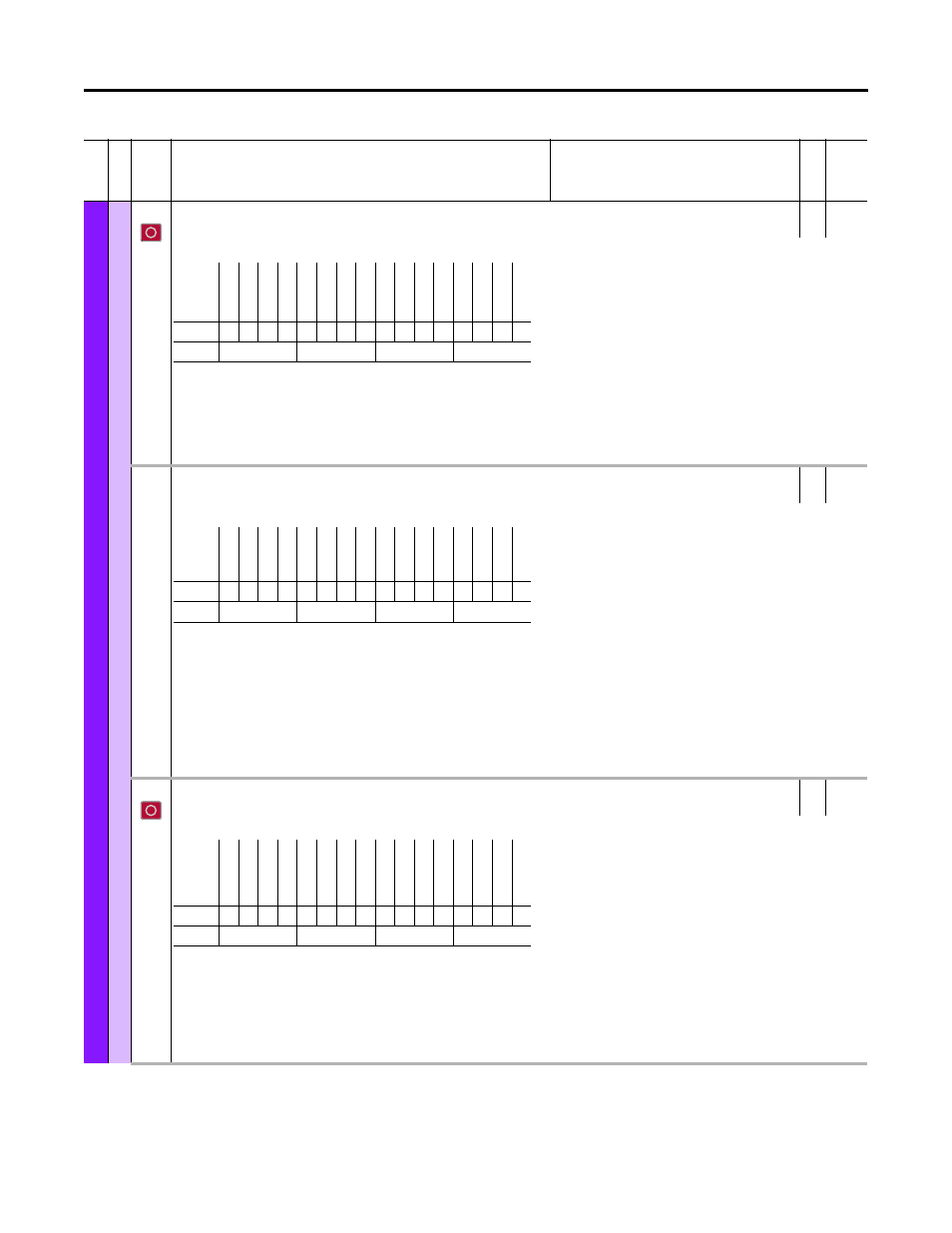

FB0 Inc Cfg

Feedback 0 Incremental Configuration

RW 16-bit

Integer

Configures Incremental Feedback for the feedback 0 device.

Bit 0 “Z Chan Enbl” – When set, Channel Z is also monitored for Phase Loss. When cleared, Channel Z is ignored for Phase Loss detection.

Only used if [FB0 Device Sel] = “Inc A B Z.”

Bit 1 “A Chan Only” – When set, logic monitors only channel A. When clear, logic monitors both A and B.

Bit 2 “Edge Mode” – When set, speed calc uses AB edge data. When clear, speed calc does not use AB edge data.

Bit 4 “Single Ended” – This bit has to be set if the connected A Quad B encoder has single ended signals. For these encoders, the Phase Loss detection is switched off.

17

FB0 Inc Sts

Feedback 0 Incremental Status

RO

16-bit

Integer

Displays Incremental Feedback status for the feedback 0 device.

Bit 0 “Z Chan Enbl” – Indicates that Channel Z is monitored for Phase Loss. Only used if [FB0 Device Sel] = “Inc A B Z.”

Bit 1 “A Chan Only” – Indicates only A channel is monitored, B channel not used.

Bit 2 “A Input” – State of encoder A input signal

Bit 3 “A Not Input” – State of encoder A Not input signal

Bit 4 “B Input” – State of encoder B input signal

Bit 5 “B Not Input” – State of encoder B Not input signal

Bit 6 “Z Input” – State of encoder Z input signal

Bit 7 “Z Not Input” – State of encoder Z Not input signal

20

FB0 SSI Cfg

Feedback 0 SSI Configuration

RW 16-bit

Integer

Configures the communication to a SSI encoder for the feedback 0 device. Transmission format: [MSB...Position...LSB], [Error Bit]*, [Parity Bit]*.

Bit 0 “Parity Bit” – If set, SSI encoder has to support a parity bit (even parity).

Bit 2 “Gray Code” – Enables the gray to binary conversion of the position.

Bit 3 “Err Bit Enbl” – If set, there is an error bit transmitted by the encoder.

Bit 4 “DblWordQuery” – If set, a Double Word Query is executed at startup which means that the same position is transmitted twice by the encoder. If the two

positions are not identical, the “Comm” error bit in [FB0 Sts] is set. This bit only needs to be cleared if the encoder does not support Double Word Query and it does

not send zeros instead of the second position (which it actually should according to the SSI specification).

Fi

le

Grou

p

No.

Display Name

Full Name

Description

Values

Re

ad

-W

ri

te

Da

ta

T

ype

Options

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Si

ngl

e E

nde

d

Re

ser

ve

d

Edge Mod

e

A Chan Only

Z Ch

an E

nbl

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

Bit

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = Condition False

1 = Condition True

Options

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Re

se

rv

ed

Z N

ot

In

pu

t

Z Inpu

t

B N

ot Inpu

t

B Inp

ut

A Not

Input

A In

put

A Chan Only

Z Cha

n En

bl

Default

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = Condition False

1 = Condition True

Options

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Re

ser

ve

d

Dbl

W

or

dQ

uer

y

Er

r B

it E

nb

l

Gr

ay

C

ode

Re

ser

ve

d

Pa

rit

y B

it

Default

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

Bit

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

0 = Condition False

1 = Condition True