Ez80® cpu instruction set description, Ez80, Cpu instruction set description – Zilog EZ80F916 User Manual

Page 86

eZ80

®

CPU

User Manual

UM007715-0415

CPU Instruction Set

77

eZ80

®

CPU Instruction Set Description

The following pages provide detailed descriptions of the assembly language instructions

available with the eZ80

®

CPU. Some CPU-based products may not support all instruc-

tions, registers, operating modes, etc. Refer to the

product

specifications

for information on CPU usage. The instruction set descriptions on the fol-

lowing pages are organized alphabetically by mnemonic.

eZ80

®

CPU Instruction Cycle Times

The instruction execution cycle time information provided for each of the following CPU

instructions refers to the bus cycles required to execute the instruction. This cycle time

information appears in the Attributes tables under the heading Cycle. The number of clock

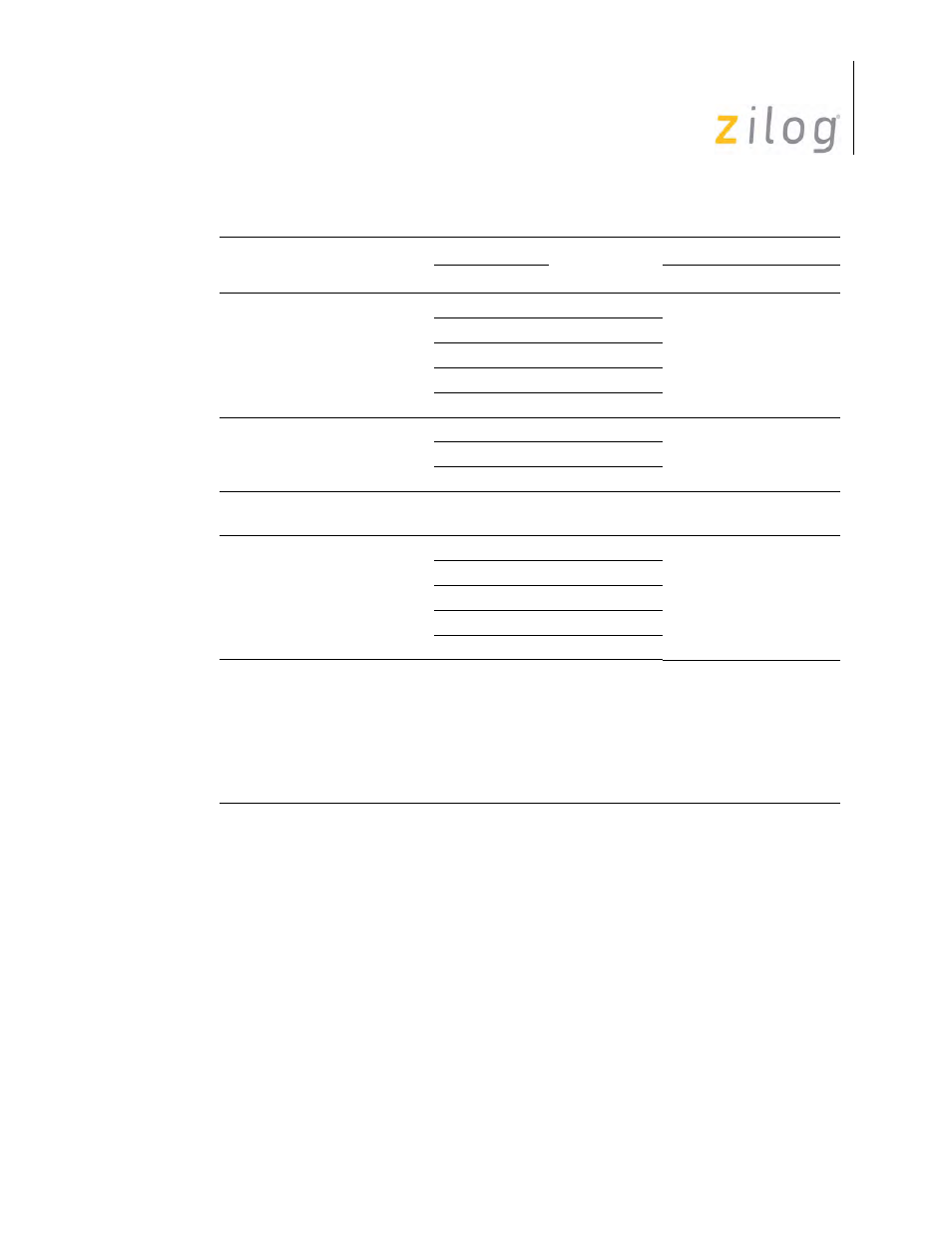

SUB

A,s

A A – s

(HL)

96

* * *

V

1 *

ir

DD/FD 94-95

(IX/Y+d) DD/FD 96 dd

n

D6

r

90-97

TST

A,s

A AND s

(HL)

ED 34

* * 1

P

0 0

n

ED 64

r

ED 04-3C

TSTIO

n

{0000h, C} AND n

ED 74

* * 1

P

0 0

XOR

A,s

A A XOR s

(HL)

AE

* * 0

P

0 0

ir

DD/FD AC–AD

(IX/Y+d) DD/FD AE dd

n

EE

r

A8-AF

Table 37. Instruction Summary (Continued)

Instruction and Operation

Address Mode

Opcode(s)

(Hex)

Flags Affected

Dest Source

S

Z

H

P/V

N

C

Note: *This flag value is a function of the result of the affected operation.

— = No Change.

0 = Set to 0.

1 = Set to 1.

V = Set to 1 if overflow occurs.

X = Undetermined.

P = Set to the parity of the result (0 if odd parity, 1 if even parity).

IEF2 = The value of Interrupt Enable Flag 2.