Zilog EZ80F916 User Manual

Page 13

eZ80

®

CPU

User Manual

UM007715-0415

Architectural Overview

4

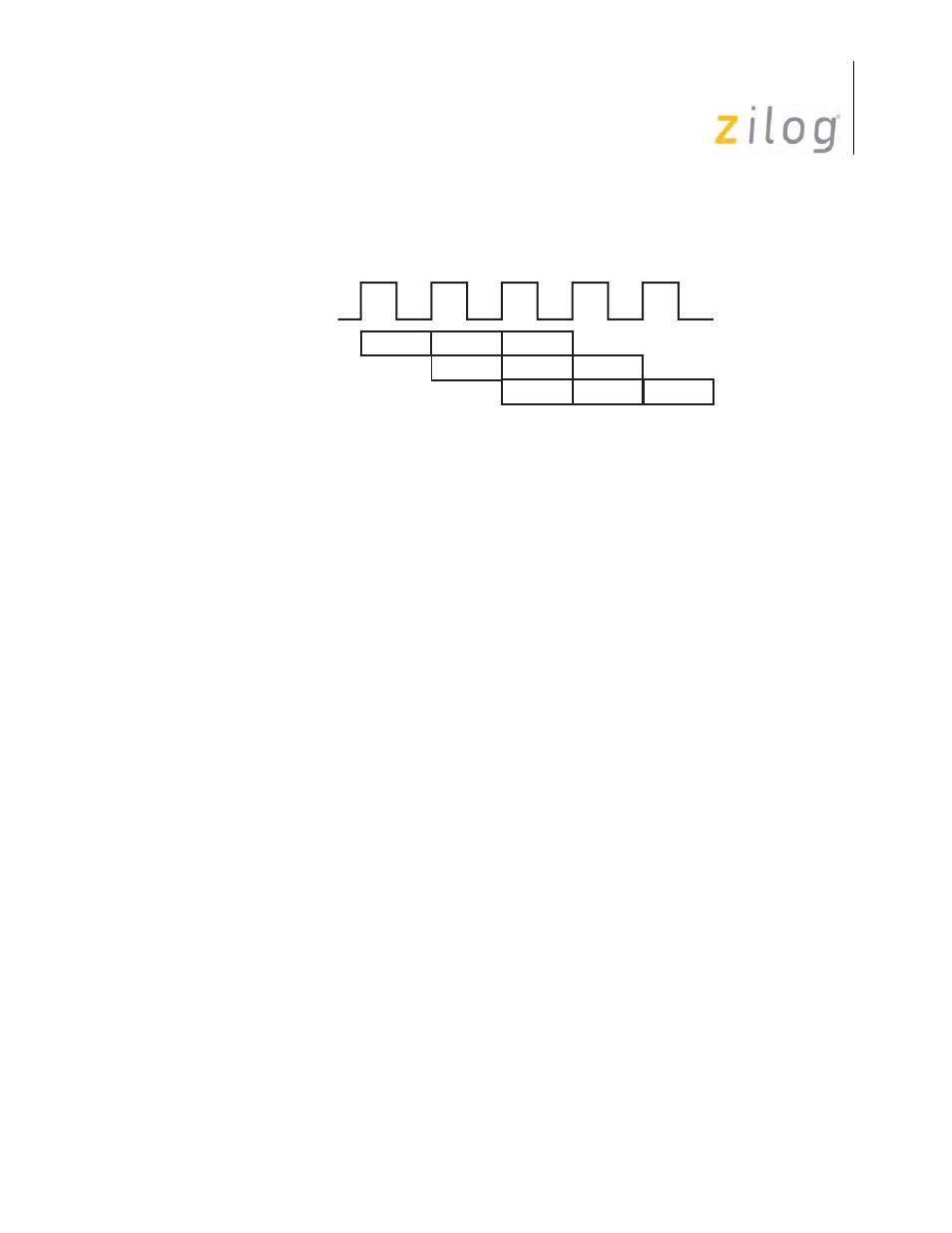

while it executes the current instruction as displayed in

. The CPU operates on

multiple instructions simultaneously to improve operating efficiency.

In

, the pipelining process is demonstrated using a series of instructions. The first

LD

instruction prefetches its opcode and first operand during the decode and execute

phases of the preceding INC instruction. However, the second LD instruction in the

sequence only prefetches its opcode. The bus WRITE during the execute phase of the first

LD

instruction prevents the pipeline from prefetching the first operand of the next instruc-

tion. Thus, the number of bytes prefetched is a function of the command currently execut-

ing in the CPU.

When a control transfer takes place, the Program Counter (PC) does not progress sequen-

tially. Therefore, the pipeline must be flushed. All prefetched values are ignored. Control

transfer can occur because of an interrupt or during execution of a Jump (JP), CALL,

Return (RET), Restart (RST), or similar instruction. After the control transfer instruction

is executed, the pipeline must start over to fetch the next operand.

Figure 2. Pipeline Overview

System Clock

Instruction 1

Instruction 2

Instruction 3

Fetch

Decode Execute

Fetch

Decode Execute

Fetch

Decode Execute