Srl (hl), Operation description, Condition bits affected attributes – Zilog EZ80F916 User Manual

Page 361

eZ80

®

CPU

User Manual

UM007715-0415

CPU Instruction Set

352

SRL (HL)

Shift Right Logical

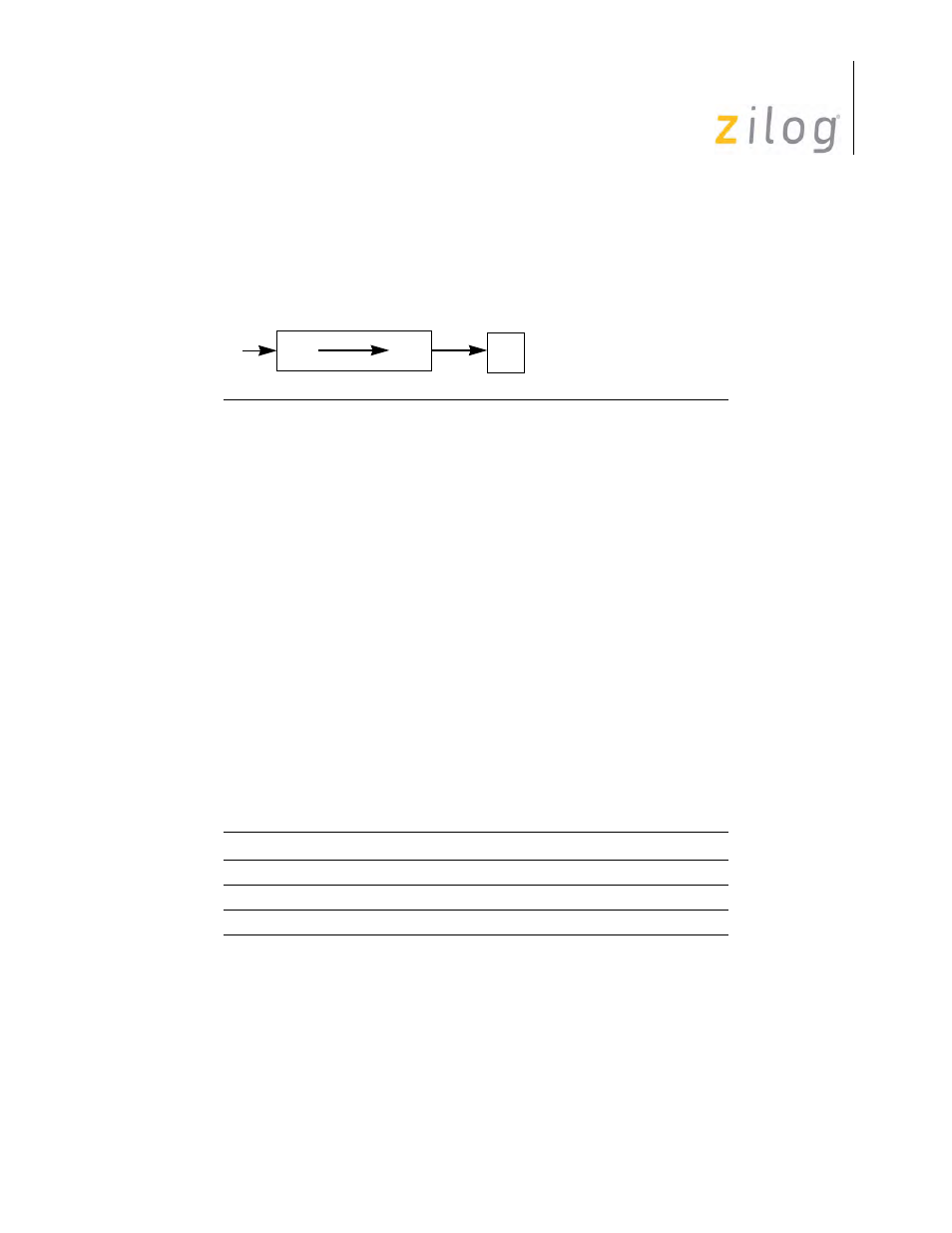

Operation

Description

The (HL) operand is an 8-bit value at the memory location specified by the contents of the

multibyte register (HL). The CPU manipulates the contents of this memory location, (HL),

by shifting them right one bit position. The CPU next copies the contents of bit 0 into the

Carry Flag and resets bit 7.

Condition Bits Affected

Attributes

S

Set if result is negative; reset otherwise.

Z

Set if result is 0; reset otherwise.

H

Reset.

P/V

Set if parity is even; reset otherwise.

N

Reset.

C

Data from bit 0 of the source.

Mnemonic Operand

ADL Mode Cycle

Opcode (hex)

SRL

(HL)

X

5

CB, 3E

SRL.S

(HL)

1

6

52, CB, 3E

SRL.L

(HL)

0

6

49, CB, 3E

C

7

0

(HL)

0

This manual is related to the following products: