Ez80, 0ddh, 0cbh – Zilog EZ80F916 User Manual

Page 389

UM007715-0415

Opcode Maps

eZ80

®

CPU

User Manual

380

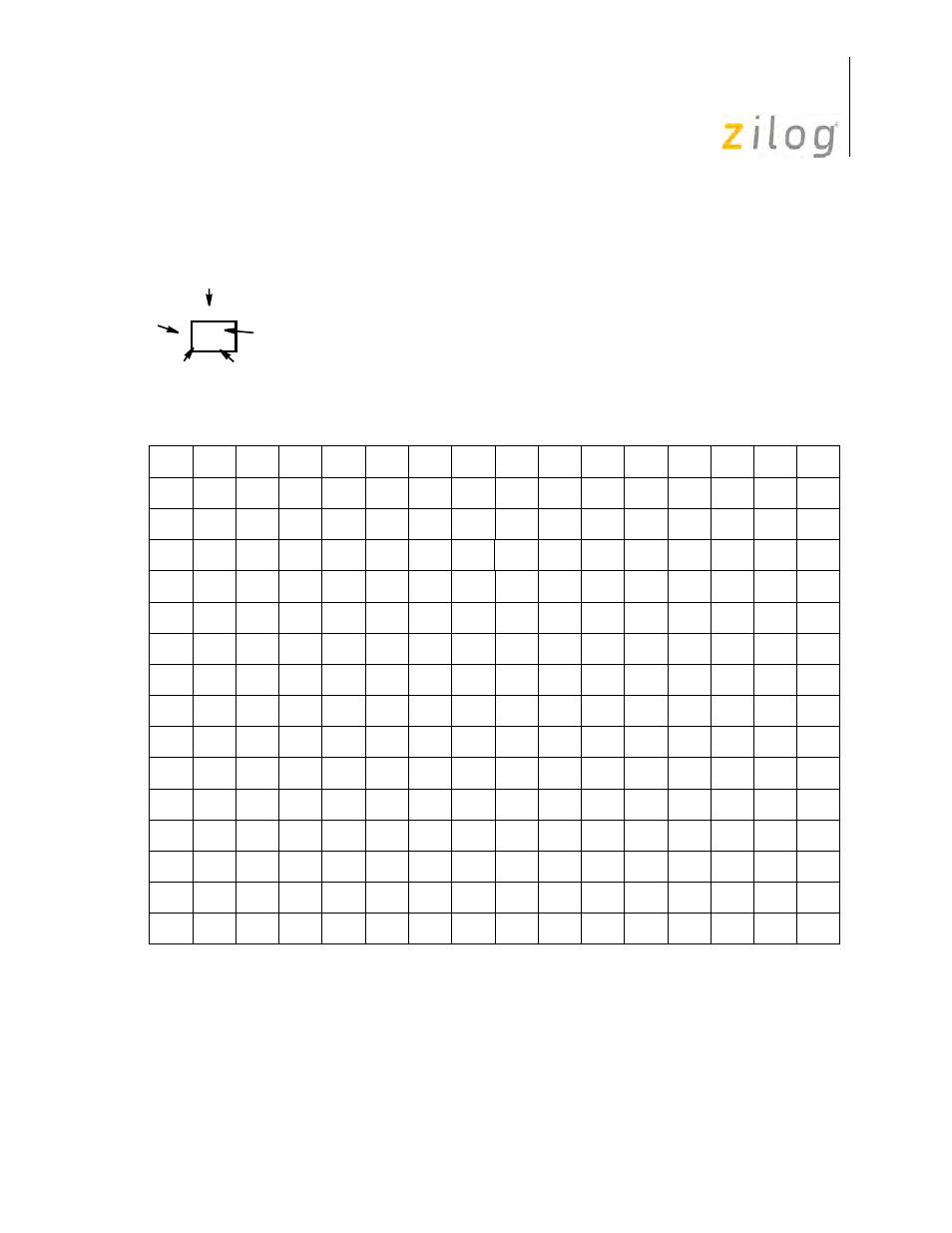

Table 111. Opcode Map—Fourth Byte After

0DDh

,

0CBh

, and

dd

Lower Nibble (Hex)

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Upp

er Ni

bbl

e (H

ex)

0

RLC

(IX+d)

RRC

(IX+d)

1

RL

(IX+d)

RR

(IX+d)

2

SLA

(IX+d)

SRA

(IX+d)

3

SRL

(IX+d)

4

BIT 0,

(IX+d)

BIT 1,

(IX+d)

5

BIT 2,

(IX+d)

BIT 3,

(IX+d)

6

BIT 4,

(IX+d)

BIT 5,

(IX+d)

7

BIT 6,

(IX+d)

BIT 7,

(IX+d)

8

RES 0,

(IX+d)

RES 1,

(IX+d)

9

RES 2,

(IX+d)

RES 3,

(IX+d)

A

RES 4,

(IX+d)

RES 5,

(IX+d)

B

RES 6,

(IX+d)

RES 7,

(IX+d)

C

SET 0,

(IX+d)

SET 1,

(IX+d)

D

SET 2,

(IX+d)

SET 3,

(IX+d)

E

SET 4,

(IX+d)

SET 5,

(IX+d)

F

SET 6,

(IX+d)

SET 7,

(IX+d)

Note: d = 8-bit two’s-complement displacement.

BIT

6

4

Lower Nibble of 4th Byte

Mnemonic

Second Operand

Upper

Byte

First Operand

0,(IX+d)

of Fourth

Nibble

Legend

This manual is related to the following products: