Table 108, Ez80, 0ddh – Zilog EZ80F916 User Manual

Page 386

UM007715-0415

Opcode Maps

eZ80

®

CPU

User Manual

377

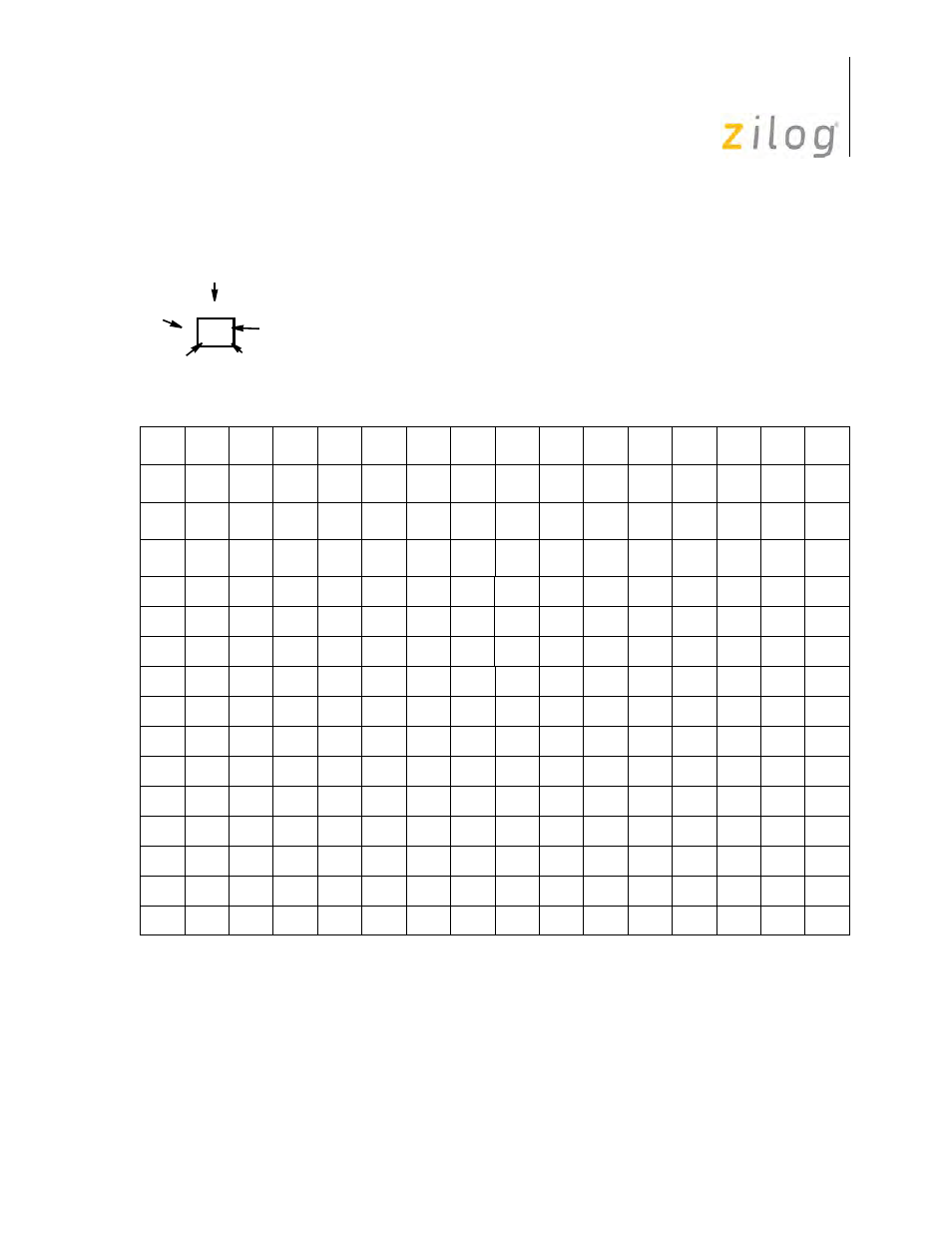

Table 108. Opcode Map—Second Opcode After

0DDh

Lower Nibble (Hex)

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

Uppe

r Nib

ble

(Hex)

0

LD BC,

(IX+d)

ADD

IX,BC

LD

(IX+d),

BC

1

LD DE,

(IX+d)

ADD

IX,DE

LD

(IX+d),

DE

2

LD

IX,

Mmn

LD

(Mmn),

IX

INC

IX

INC

IXH

DEC

IXH

LD

IXH,n

LD HL,

(IX+d)

ADD

IX,IX

LD

IX,

(Mmn)

DEC

IX

INC

IXL

DEC

IXL

LD

IXL,n

LD

(IX+d),

HL

3

LD IY,

(IX+d)

INC

(IX+d)

DEC

(IX+d)

LD (IX

+d),n

LD IX,

(IX+d)

ADD

IX,SP

LD

(IX+d),

IY

LD

(IX+d),

IX

4

LD

B,IXH

LD

B,IXL

LD B,

(IX+d)

LD

C,IXH

LD

C,IXL

LD C,

(IX+d)

5

LD

D,IXH

LD

D,IXL

LD D,

(IX+d)

LD

E,IXH

LD

E,IXL

LD E,

(IX+d)

6

LD

IXH,B

LD

IXH,C

LD

IXH,D

LD

IXH,E

LD

IXH,IXH

LD

IXH,IXL

LD H,

(IX+d)

LD

IXH,A

LD

IXL,B

LD

IXL,C

LD

IXL,D

LD

IXL,E

LD

IXL,IXH

LD

IXL,IXL

LD L,

(IX+d)

LD

IXL,A

7

LD

(IX+d),B

LD

(IX+d),C

LD

(IX+d),D

LD

(IX+d),E

LD

(IX+d),H

LD

(IX+d),L

LD

(IX+d),A

LD

A,IXH

LD

A,IXL

LD A,

(IX+d)

8

ADD

A,IXH

ADD

A,IXL

ADD A,

(IX+d)

ADC

A,IXH

ADC

A,IXL

ADC A,

(IX+d)

9

SUB

A,IXH

SUB

A,IXL

SUB A,

(IX+d)

SBC

A,IXH

SBC

A,IXL

SBC A,

(IX+d)

A

AND

A,IXH

AND

A,IXL

AND A,

(IX+d)

XOR

A,IXH

XOR

A,IXL

XOR A,

(IX+d)

B

OR

A,IXH

OR

A,IXL

OR A,

(IX+d)

CP

A,IXH

CP

A,IXL

CP A,

(IX+d)

C

D

E

POP

IX

EX

(SP),IX

PUSH

IX

JP

(IX)

F

LD

SP,IX

Note: n = 8-bit datA; Mmn = 16- or 24-bit addr or data; d = 8-bit two’s-complement displacement.

LD

9

F

Mnemonic

Second Operand

First Operand

SP,IX

Lower Nibble of 2nd Opcode

Upper

Opcode

of Second

Nibble

Legend