Operation, Description, Condition bits affected – Zilog EZ80F916 User Manual

Page 138

eZ80

®

CPU

User Manual

UM007715-0415

CPU Instruction Set

129

DAA

Decimal Adjust Accumulator

Operation

A Decimal Adjust (A)

Description

This instruction conditionally adjusts the accumulator, A, following addition and subtrac-

tion operations on binary-coded-decimal (BCD) values. For addition (ADD, ADC, INC)

or subtraction (SUB, SBC, DEC, NEG),

indicates the operation performed by

the DAA instruction.

Condition Bits Affected

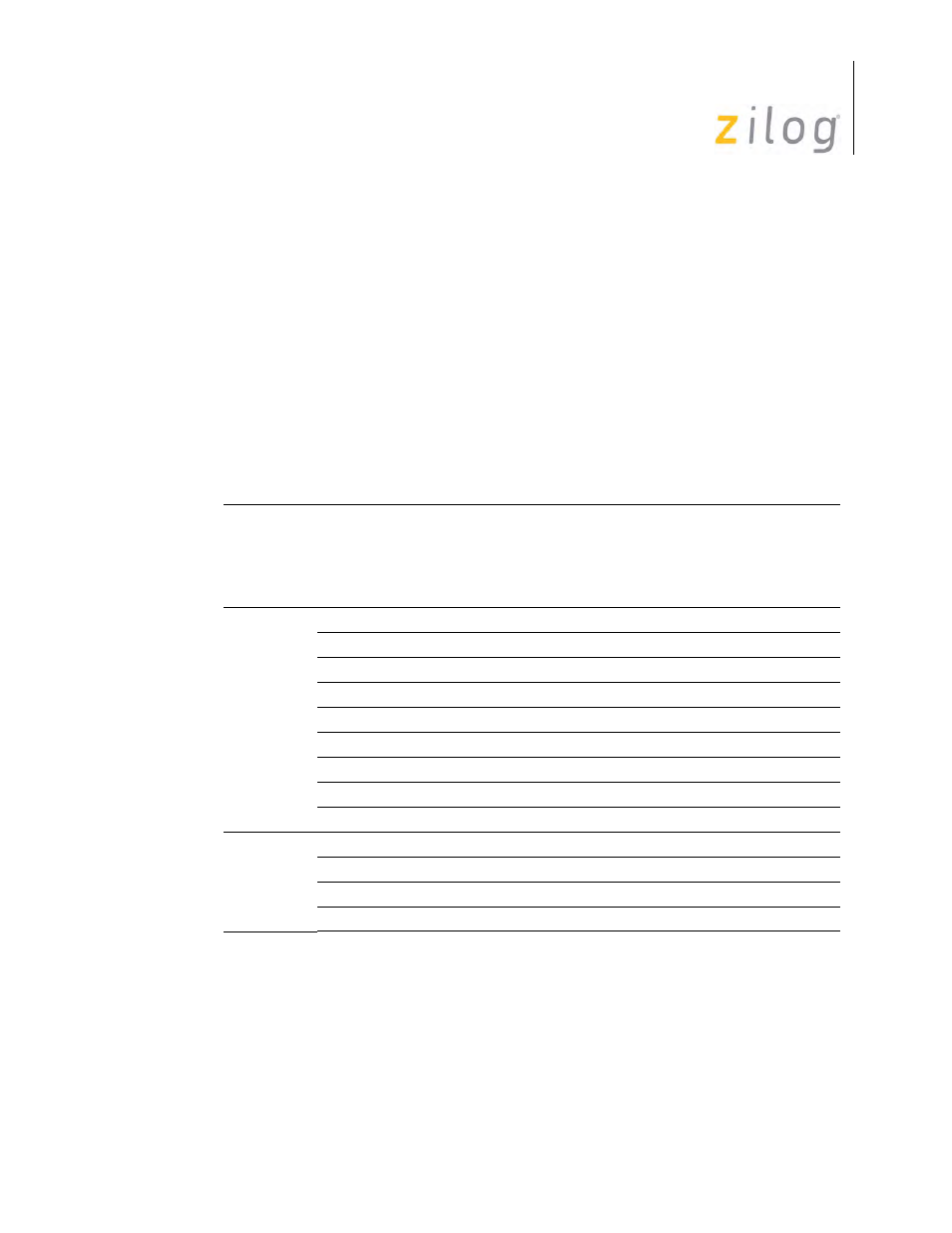

Table 51. Operations of the DAA Instruction

Operation

C Before

DAA

Hex

Value in

Upper

Digit

(Bits 7:4)

H Before

DAA

Hex

Value in

Lower

Digit

(Bits 3:0)

Number

Added to

Byte

C After

DAA

H After

DAA

ADD

, ADC,

or INC

0

0–9

0

0–9

00

0

0

0

0–8

0

A–F

06

0

1

0

0–9

1

0–3

06

0

0

0

A–F

0

0–9

60

1

0

0

9–F

0

A–F

66

1

1

0

A–F

1

0–3

66

1

0

1

0–2

0

0–9

60

1

0

1

0–2

0

A–F

66

1

1

1

0–3

1

0–3

66

1

0

SUB

, SBC,

DEC

, or

NEG

0

0–9

0

0–9

00

0

0

0

0–8

1

6–F

FA

0

0

1

7–F

0

0–9

A0

1

0

1

6–F

1

6–F

9A

1

0

S

Set if the msb of the result is 1 after the operation; reset

otherwise.

Z

Set if result is 0; reset otherwise.

H

See