Architectural overview, Processor description – Zilog EZ80F916 User Manual

Page 11

eZ80

®

CPU

User Manual

UM007715-0415

Architectural Overview

2

Architectural Overview

The eZ80

®

CPU is Zilog's next-generation Z80 processor core. It is the basis of a new

family of integrated microcontrollers and includes the following features:

•

Upward code-compatible from Z80 and Z180 products.

•

Several address-generation modes, including 24-bit linear addressing.

•

24-bit registers and ALU.

•

8-bit data path.

•

Single-cycle fetch.

•

Pipelined fetch, decode, and execute.

Processor Description

The eZ80

®

CPU is an 8-bit microcontroller that performs certain 16- or 24-bit operations.

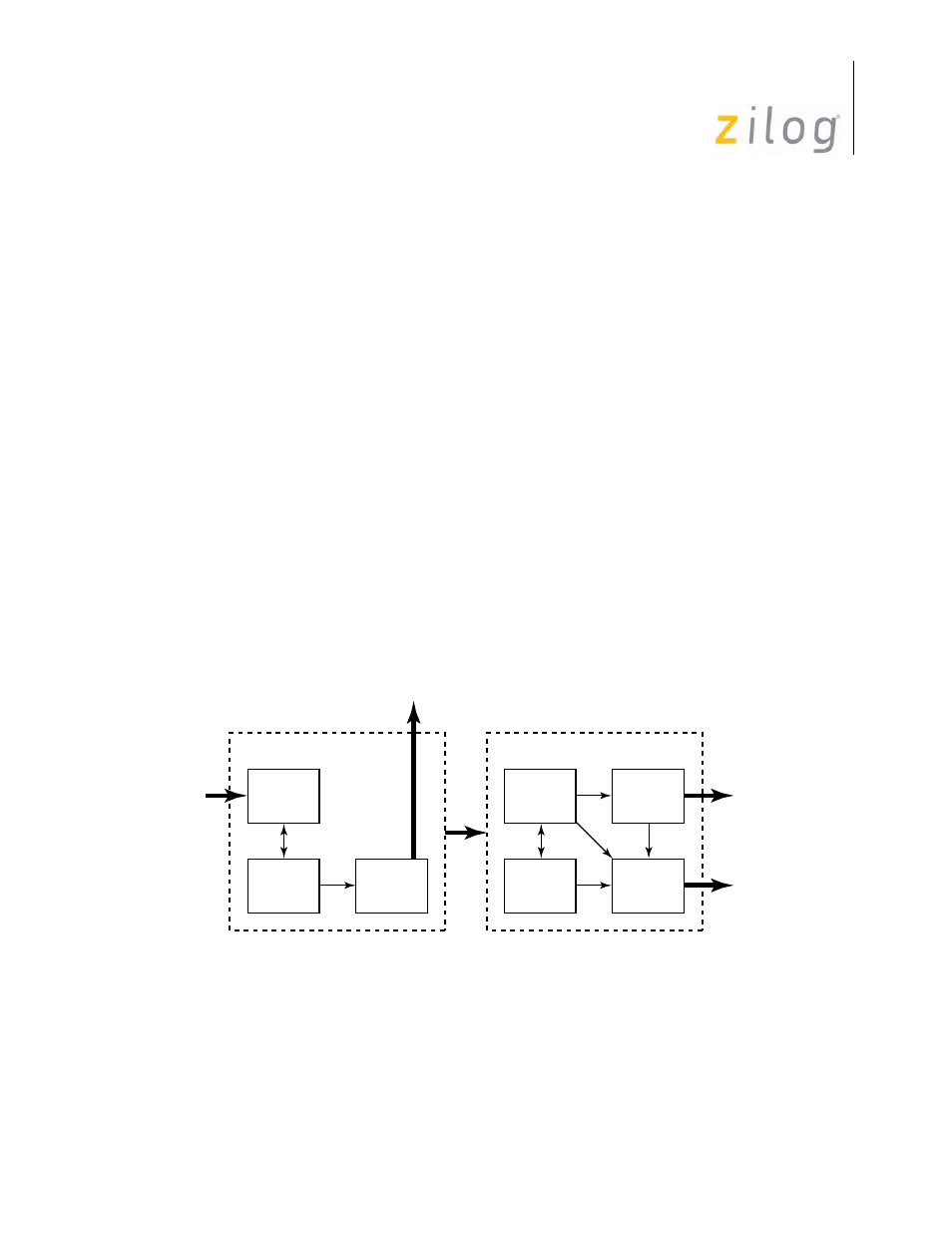

A simplified block diagram of the CPU is displayed in

. Understanding the sepa-

ration between the control block and the data block is helpful toward understanding the

two eZ80

®

memory modes—Z80 mode and ADDRESS AND DATA LONG (ADL)

mode.

Instruction Fetch

The instruction fetch block contains a state machine which controls the READs from

memory. It fetches opcodes and operands and keeps track of the start and end of each

instruction. An instruction fetch block stores opcodes during external memory READs

Figure 1. eZ80

®

CPU Block Diagram

Control Block

Data Block

I/O Control

DATA

DATA

ADDR

Instruction

Fetch

Mode

Control

Op Code

Decoder

CPU

Registers

Address

Generator

ALU

Data

Selector