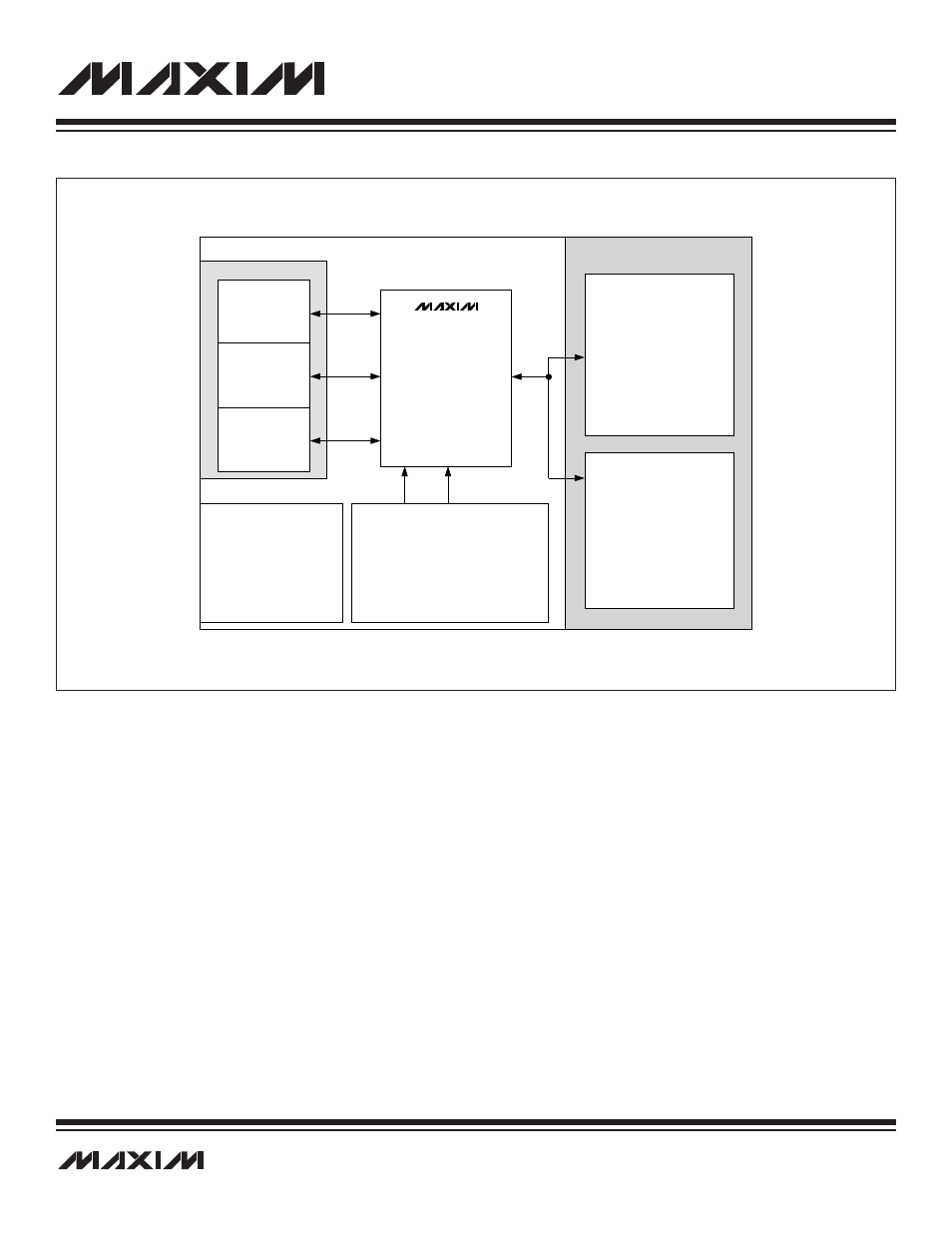

2 instruction set, 2 instruction set -4, Figure 2-1. maxq7667 block diagram -4 – Maxim Integrated MAXQ7667 User Manual

Page 9: Maxq7667 user’s guide

2.1.2 Instruction Set

As part of the MAXQ family, the MAXQ7667 uses the standard 16-bit MAXQ20 instruction set, with all instructions a fixed 16 bits in

length. A register-based, transport-triggered architecture allows all instructions to be coded as simple transfer operations. All instruc-

tions reduce to either writing an immediate value to a destination register or memory location or moving data between registers and/or

memory locations.

This simple top-level instruction decoding allows all instructions to be executed in a single cycle. Since all CPU operations are per-

formed on registers only, any new functionality can be added by simply adding new register modules. The simple instruction set also

provides maximum flexibility for code optimization by a compiler.

___________________________________________________________________________________________________________

2-4

MAXQ7667 User’s Guide

Figure 2-1. MAXQ7667 Block Diagram

16-BIT HARVARD

MAXQ RISC CPU

•

16 ALU REGISTERS

•

MMU

•

HW MULTPLY/ACCUM

•

INTERRUPT CONTROL

•

16-WORD HW STACK

•

HARVARD ARCHITECTURE

MEMORY MODULE

CORE MODULES

CLOCK/CRYSTAL/

TIMER MODULE

•

INTERNAL 16MHz (MAX)

OSCILLATOR

•

EXTERNAL XTAL OSC

•

WATCHDOG TIMER

•

SCHEDULE TIMER

POWER MANAGEMENT

MODULE

•

+5V I/O REGULATOR

•

+3.3V ANALOG REGULATOR

•

+2.5V CORE REGULATOR

•

POWER-ON RESET

•

SUPPLY BROWNOUT DETECTORS

PERIPHERAL MODULES

GENERAL-PURPOSE

PERIPHERALS

•

3 16-BIT TIMER/PWMs

•

2 8-BIT I/O PORTS

•

UART WITH LIN 2.0 H/W

•

SPI INTERFACE

•

JTAG INTERFACE

•

12-BIT, 5-CHANNEL ADC

•

VOLTAGE REFERENCE

MAXQ7667

APPLICATION-SPECIFIC

PERIPHERALS

•

VARIABLE GAIN LNA

•

16-BIT SIGMA-DELTA ADC

•

DIGITAL BANDPASS FILTER

•

DIGITAL LOWPASS FILTER

•

LP FILTER FIFO

•

PLL FREQUENCY GENERATOR

•

BURST GENERATOR

UTILITY ROM

DATA RAM

4KB

(2KWORD)

FLASH ROM

32KB

(16KWORD)