2 spi control register, 2 spi control register (spicn) -7, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 169

9-7

___________________________________________________________________________________________________________

MAXQ7667 User’s Guide

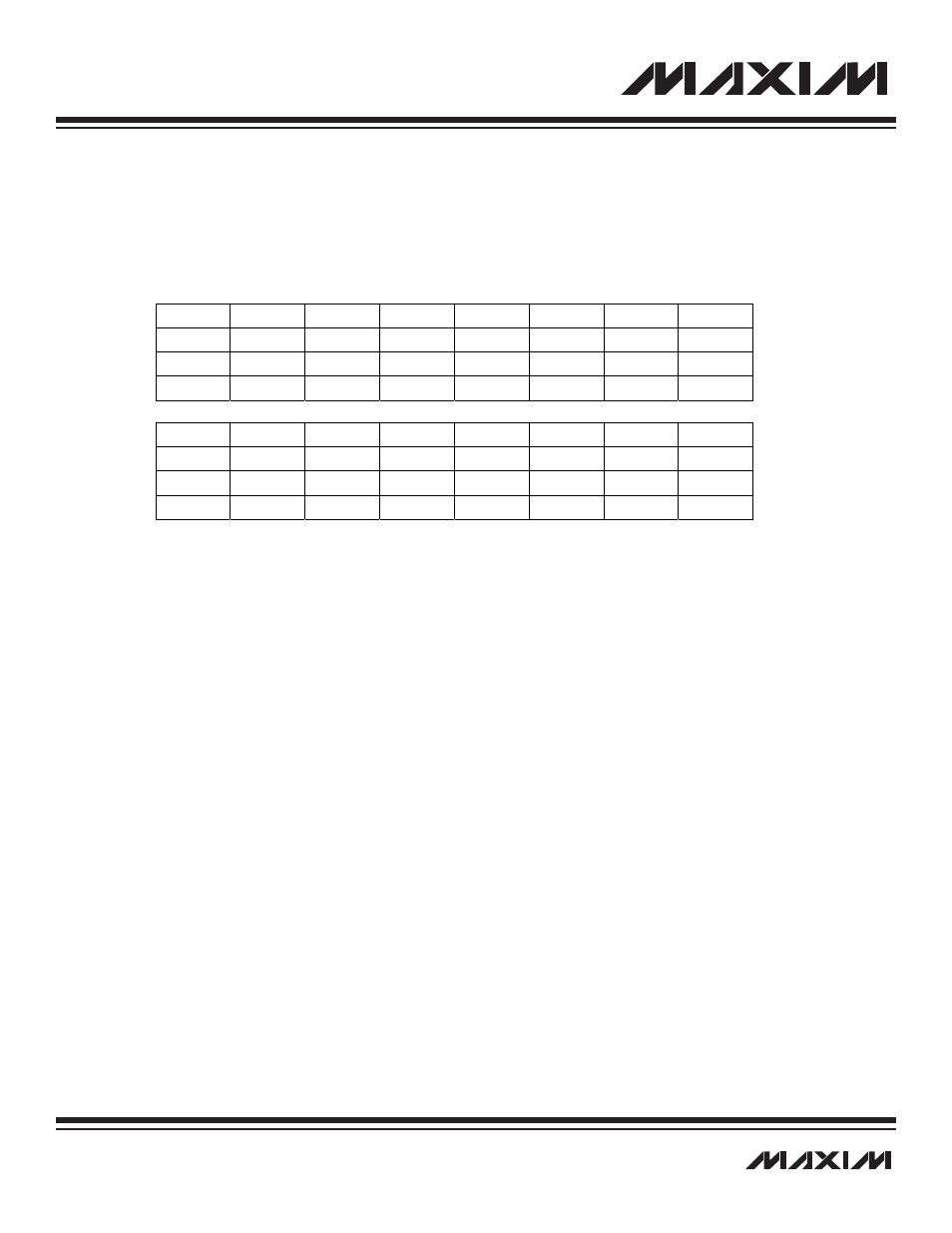

9.1.1.2 SPI Control Register (SPICN)

The SPI control register (SPICN) contains both mode control and status flags to monitor the operation of the SPI port. This register is

byte accessed

Register Description:

SPI Control Register

Register Name:

SPICN

Register Address:

Module 01h, Index 07h

Bits 15 to 8: Reserved. Read 0, write ignored.

Bit 7: SPI Transfer Busy Flag (STBY). This flag indicates when an SPI transfer cycle is in progress. This bit is set and cleared under

hardware control. All forms of reset clear this bit.

0 = SPI module is idle—no transfer in progress.

1 = SPI transfer in progress.

Bit 6: SPI Transfer Complete Flag (SPIC). This flag detects the completion of an SPI transfer. For a write transfer, the SPIC flag is set

when the last bit is shifted out of the SPIB. For a read transfer, this flag is set when the SPI port read buffer is loaded with new data.

This flag reports:

0 = No SPI transfer, since the bit was cleared.

1 = SPI transfer complete.

All forms of reset clear this bit. Writing a 0 to the bit also clears it. This bit is read- and write-access enabled and can be set by indi-

vidual bit write operations.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

STBY

SPIC

ROVR

WCOL

MODF

MODFE

MSTM

SPIEN

Reset

0

0

0

0

0

0

0

0

Access

r

rw

rw

rw

rw

rw

rw

rw

r = read, w = write