12 external interrupt ed, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 88

5-13

__________________________________________________________________________________________________________

MAXQ7667 User’s Guide

5.2.12 External Interrupt Edge Select Register (Port 1) (EIES1)

Register Description:

External Interrupt Edge Select Register (Port 1)

Register Name:

EIES1

Register Address:

Module 00h, Index 14h

Bits 15 to 8: Reserved. Read returns 0, write ignored.

Bit 7: Edge Select for External Interrupt 7 (IT7)

IT7 = 0: External interrupt 7 is positive-edge triggered.

IT7 = 1: External interrupt 7 is negative-edge triggered.

Bit 6: Edge Select for External Interrupt 6 (IT6)

IT6 = 0: External interrupt 6 is positive-edge triggered.

IT6 = 1: External interrupt 6 is negative-edge triggered.

Bit 5: Edge Select for External Interrupt 5 (IT5)

IT5 = 0: External interrupt 5 is positive-edge triggered.

IT5 = 1: External interrupt 5 is negative-edge triggered.

Bit 4: Edge Select for External Interrupt 4 (IT4)

IT4 = 0: External interrupt 4 is positive-edge triggered.

IT4 = 1: External interrupt 4 is negative-edge triggered.

Bit 3: Edge Select for External Interrupt 3 (IT3)

IT3 = 0: External interrupt 3 is positive-edge triggered.

IT3 = 1: External interrupt 3 is negative-edge triggered.

Bit 2: Edge Select for External Interrupt 2 (IT2)

IT2 = 0: External interrupt 2 is positive-edge triggered.

IT2 = 1: External interrupt 2 is negative-edge triggered.

Bit 1: Edge Select for External Interrupt 1 (IT1)

IT1 = 0: External interrupt 1 is positive-edge triggered.

IT1 = 1: External interrupt 1 is negative-edge triggered.

Bit 0: Edge Select for External Interrupt 0 (IT0)

IT0 = 0: External interrupt 0 is positive-edge triggered.

IT0 = 1: External interrupt 0 is negative-edge triggered.

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

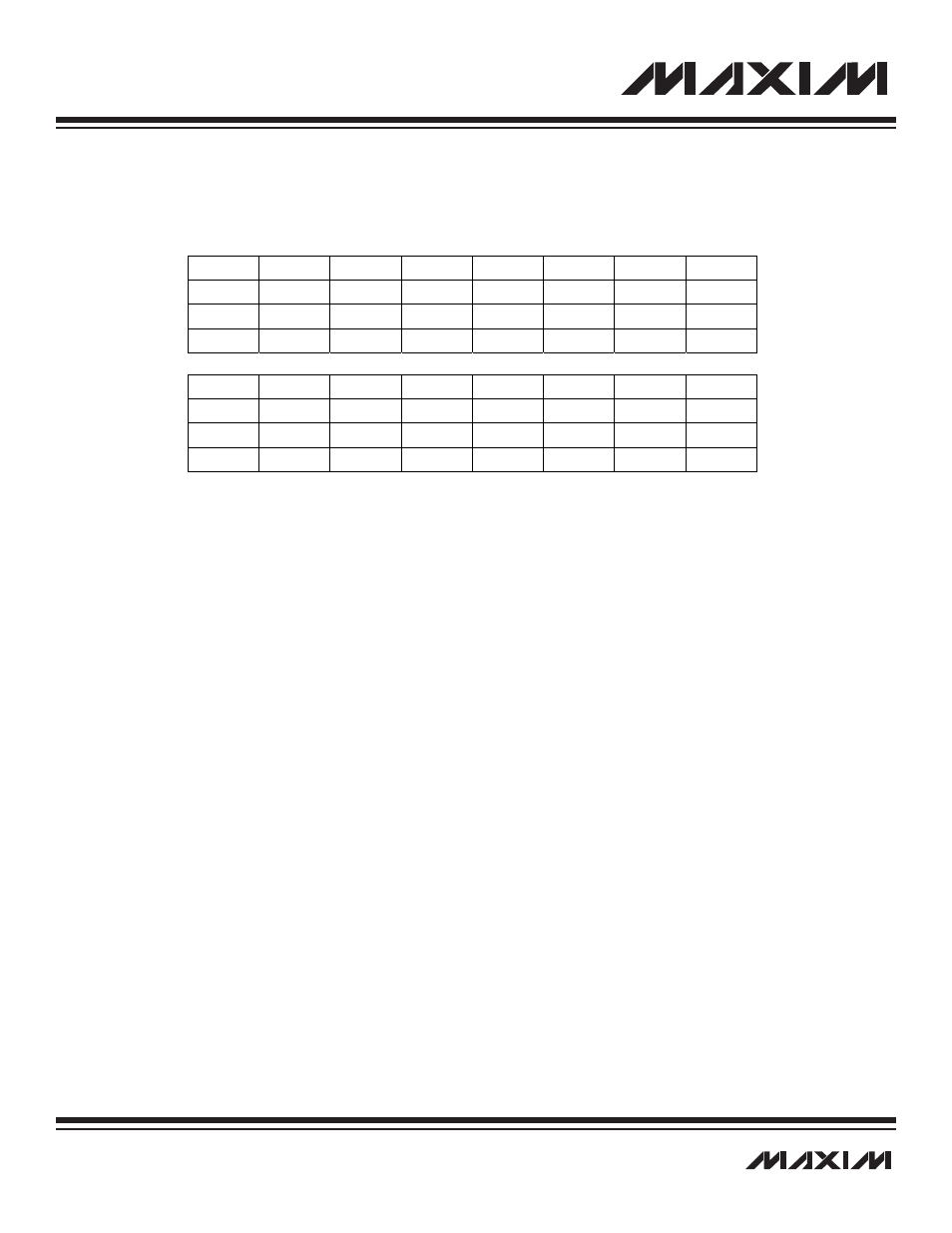

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

IT7

IT6

IT5

IT4

IT3

IT2

IT1

IT0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw