4 power-on reset, 4 power-on reset -12, Figure 16-6. maxq7667 power-on reset -12 – Maxim Integrated MAXQ7667 User Manual

Page 278: Maxq7667 user’s guide

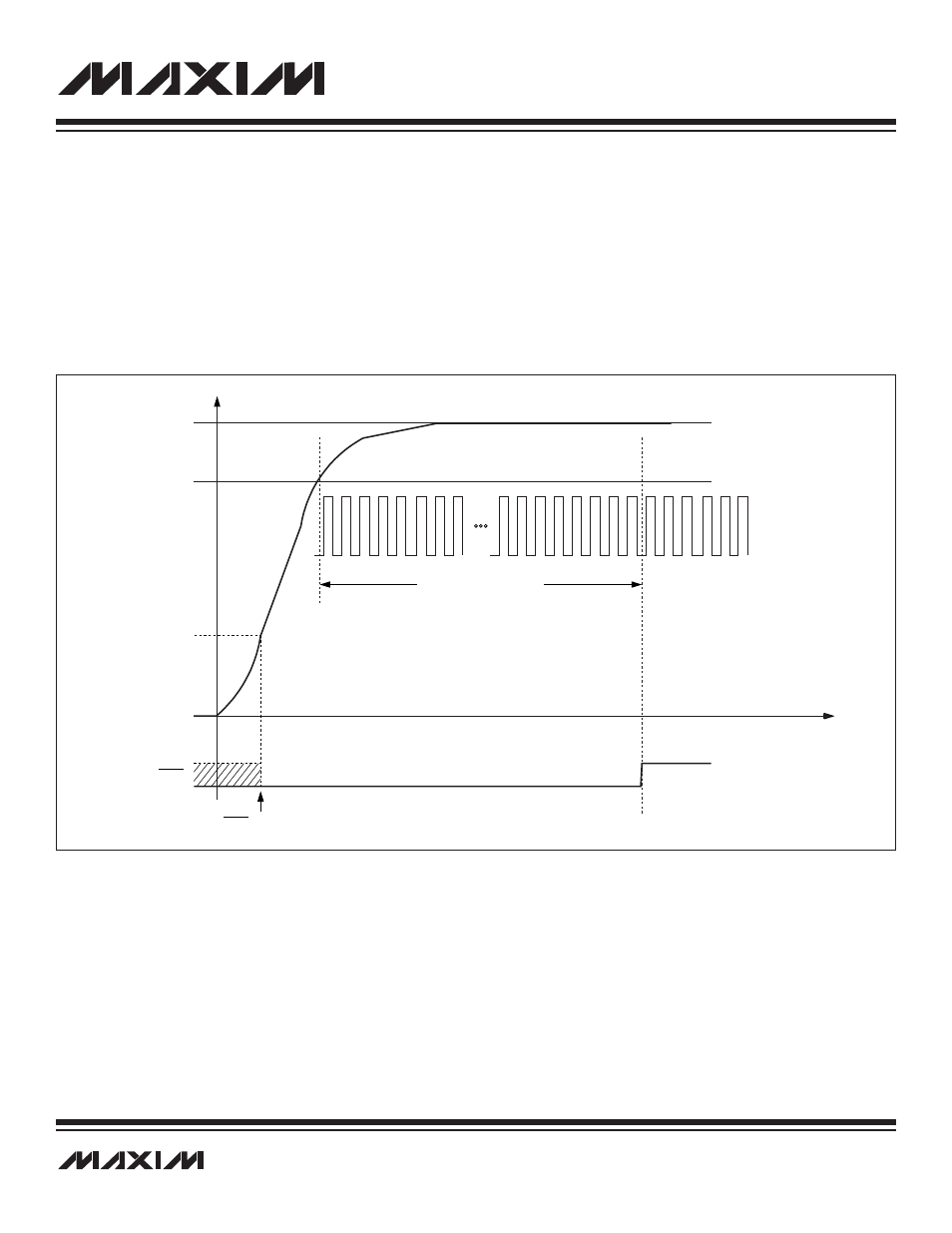

16.4 Power-On Reset

On power-up, the VDPE bit (APE.7) is automatically set to 1, enabling the DVDD reset supervisor; consequently, the internal circuitry

pulls the RESET pin low and all the internal system and peripheral registers are reset. As DVDD rises, it crosses the power-on-reset

voltage threshold level, which can be between 2.10V and 2.25V, causing the crystal warmup counter to start. The

RESET pin is held

low until the completion of the counter.

Once the crystal warmup period has elapsed, the internal circuit releases the

RESET pin. If no external circuitry is holding RESET low,

the voltage on RESET rises and software execution begins at the reset vector location 8000h (in the utility ROM). Software can deter-

mine whether a reset was caused by a power-on/brownout reset or by other forms of reset by checking the POR flag in the WDCN reg-

ister (WDCN.7). This flag is set to 1 following a power-on/brownout reset, and should be cleared by software after it has been checked.

_________________________________________________________________________________________________________

16-12

MAXQ7667 User’s Guide

Figure 16-6. MAXQ7667 Power-On Reset

CRYSTAL WARMUP DELAY

65,535 CYCLES

NOMINAL DVDD

(+2.5V)

DVDD RESET

THRESHOLD

(2.10V TO 2.25V)

DGND

1V

RESET

RESET TRACKS DVDD UP TO THIS POINT.