2 burst transmission and, 3 echo burst transmission, 1 burst pulse-width hig – Maxim Integrated MAXQ7667 User Manual

Page 288: 2 burst transmission and echo reception pinouts -6, 1 burst pulse-width high control register (bph) -6, Table 17-1. burst transmission pinout -6, Table 17-2. echo reception pinout -6, Table 17-3. voltage reference pinout -6, Maxq7667 user’s guide, 1 burst pulse-width high control register (bph)

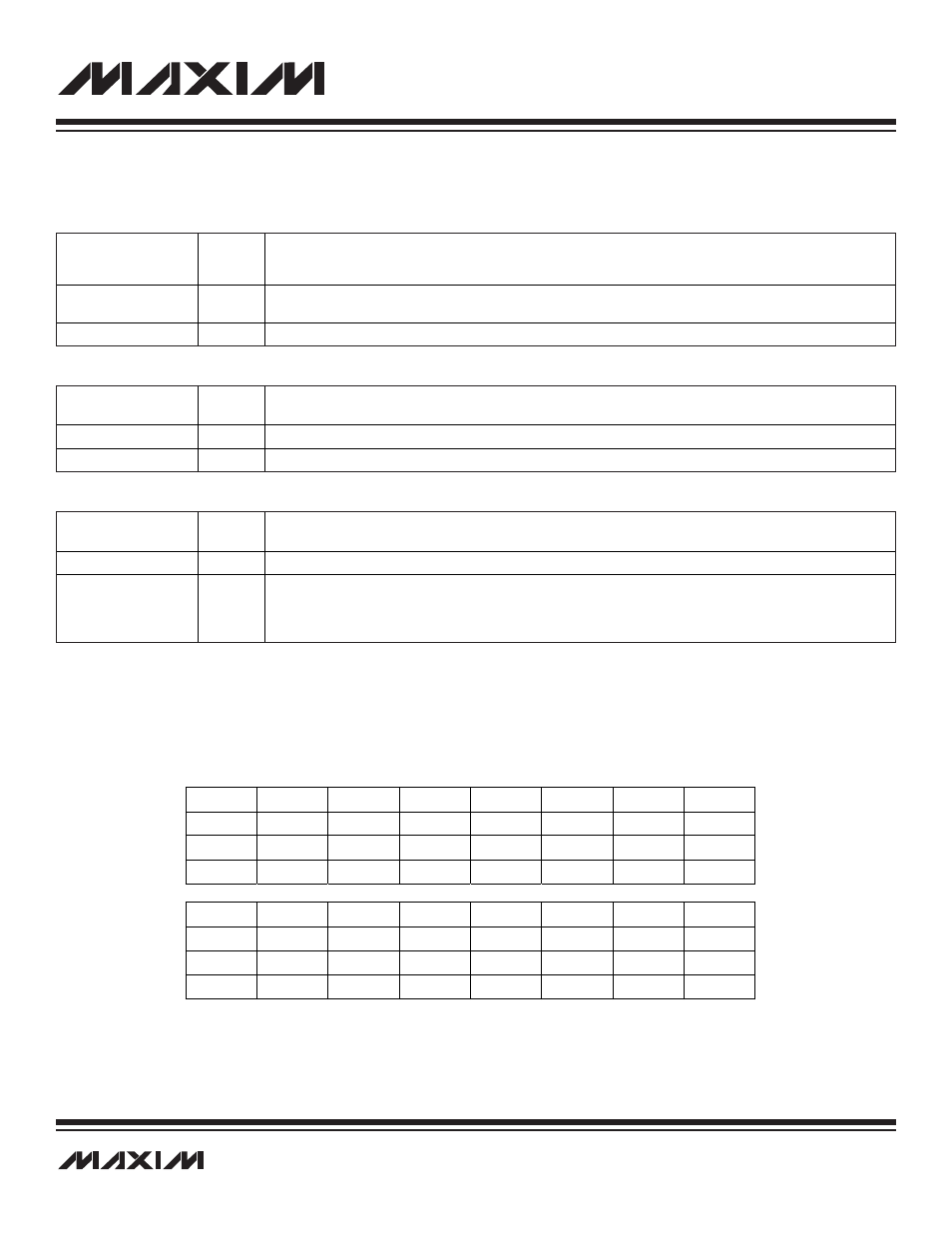

17.2 Burst Transmission and Echo Reception Pinouts

Table 17-1. Burst Transmission Pinout

Table 17-2. Echo Reception Pinout

Table 17-3. Voltage Reference Pinout

17.3 Echo Burst Transmission and Burst Echo Reception Registers

17.3.1 Burst Pulse-Width High Control Register (BPH)

Register Description:

Burst Pulse-Width High Control Register

Register Name:

BPH

Register Address:

Module 05h, Index 00h

Bit 15: Burst Start (BSTT). Setting this bit to 1 starts a burst transmission with frequency, duty cycle, and number of pulses deter-

mined by BDIV, BPH, and BCNT. This bit remains 1 until the burst transmission has completed, at which point it is automatically reset

to 0. Changing BSTT to 0 in software is blocked by hardware.

__________________________________________________________________________________________________________

17-6

MAXQ7667 User’s Guide

BURST

TRANSMISSION

SIGNAL

PIN

FUNCTION

BURST

45

Burst Output. Provides transmit pulses to ultrasonic transducer. Output polarity is programmable. Powers up in

three-state mode.

FILT

26

Filter pin for burst frequency phase-locked loop (PLL).

ECHO RECEPTION

SIGNAL

PIN

FUNCTION

ECHOP

30

Positive Echo Input. Capacitively coupled from ultrasonic transducer.

ECHON

29

Negative Echo Input. Capacitively coupled from ultrasonic transducer.

VOLTAGE

REFERENCE

PIN

FUNCTION

REFBG

35

Internal 2.5V Reference Output. Connect a minimum value of 0.47µF bypass capacitor to AGND.

REF

34

ADC Reference Input and Reference Buffer Output. This pin is for the ADC reference input. The buffer connected to

the REFBG pin must be disabled to allow the pin to accept an external reference input. Provide a bypass to AGND

with a 0.47µF capacitor. This pin requires a low ESR. This can be done by using two capacitors in parallel instead of

one, e.g., a 1µF capacitor in parallel with a 10nF capacitor instead of just a 1µF capacitor.

r = read, w = write

Note: BPH is cleared to 0000h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

BSTT

BDS

—

—

—

—

BPH9

BPH8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

r

r

r

r

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

BPH7

BPH6

BPH5

BPH4

BPH3

BPH2

BPH1

BPH0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw