3 type 2 status/control re, 1 type 2 timer/counter c, 3 type 2 status/control registers -8 – Maxim Integrated MAXQ7667 User Manual

Page 102: Maxq7667 user’s guide, 3 type 2 status/control registers

___________________________________________________________________________________________________________

6-8

MAXQ7667 User’s Guide

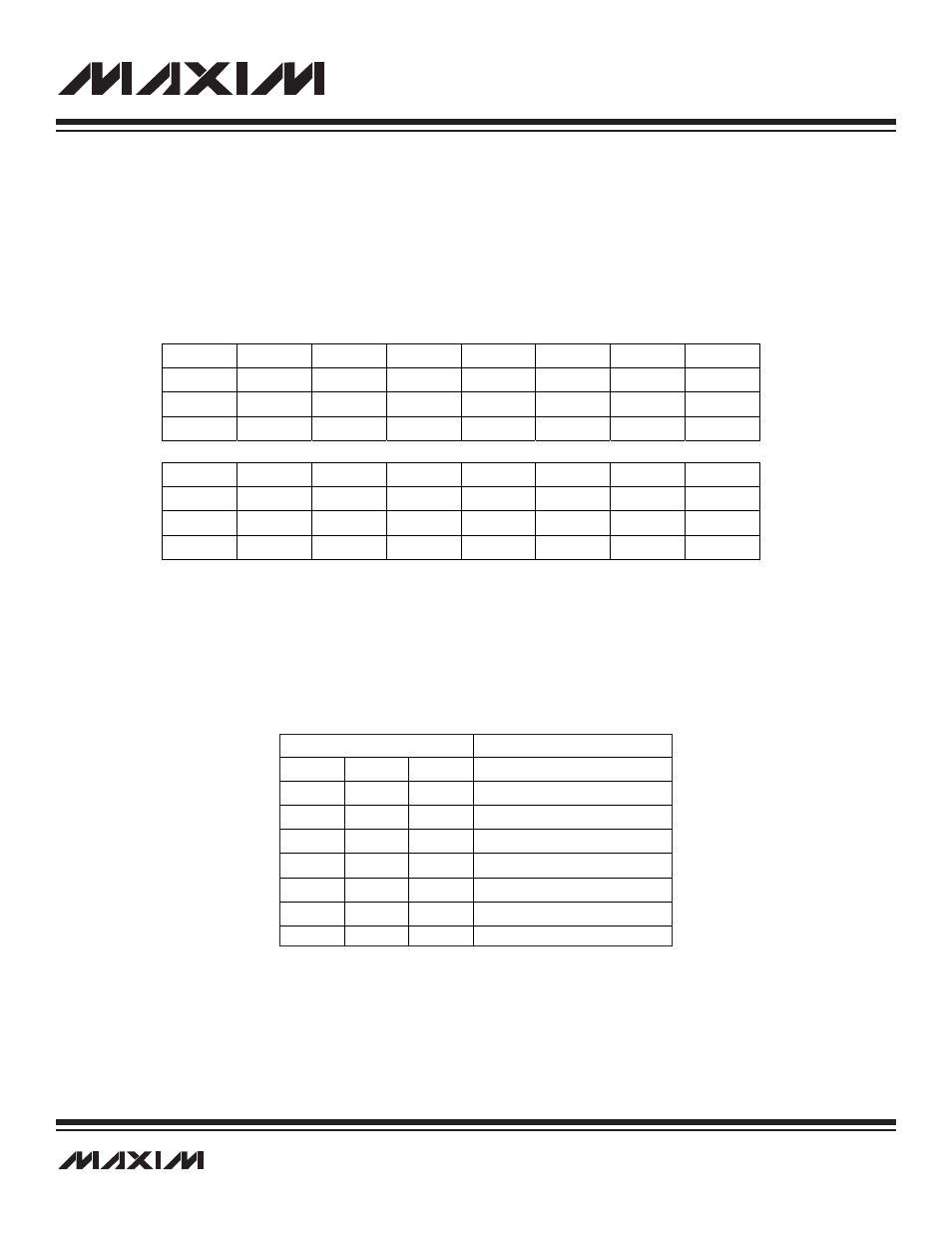

6.3 Type 2 Status/Control Registers

6.3.1 Type 2 Timer/Counter Configuration Register (T2CFGx)

Register Description:

Type 2 Timer/Counter Configuration Register

Register Name:

T2CFGx (x = 0, 1, 2)

Register Address:

T2CFG0:

Module 02h, Index 10h

T2CFG1:

Module 02h, Index 11h

T2CFG2:

Module 03h, Index 10h

Bits 15 to 8: Reserved. Read 0, write ignored.

Bit 7: Type 2 Timer Clock Input Select Bit (T2CI). Setting this bit enables an alternate input clock source to the Type 2 timer block.

The alternate input clock selection is the 32kHz clock. The alternate input clock must be sampled by the system clock, which requires

that the system clock be at least 4 x 32kHz for proper operation unless the system clock is also source from the 32kHz crystal.

Bits 6 to 4: Type 2 Timer Clock Divide Bits 2:0 (T2DIV[2:0]). These three bits select the divide ratio for the timer clock input clock

(as a function of the system clock) when operating in timer mode with T2CI = 0.

Bit 3: Type 2 Timer Mode Select (T2MD). This bit enables the dual 8-bit mode of operation. The default reset state is 0, which selects

the 16-bit mode of operation. When the dual 8-bit mode is established, the primary timer/counter (T2Hx) carries all the counter/cap-

ture functionality, while the secondary 8-bit timer (T2Lx) must operate in timer compare mode, sourcing the defined internal clock.

0 = 16-bit mode (default)

1 = dual 8-bit mode

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

T2CI

T2DIV2

T2DIV1

T2DIV0

T2MD

CCF1

CCF0

C/T2

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

T2DIV[2:0]

DIVIDE RATIO

0

0

0

1

0

0

1

2

0

1

0

4

0

1

1

8

1

0

0

16

1

0

1

32

1

1

0

64

1

1

1

128