Maxim Integrated DS5001FP User Manual

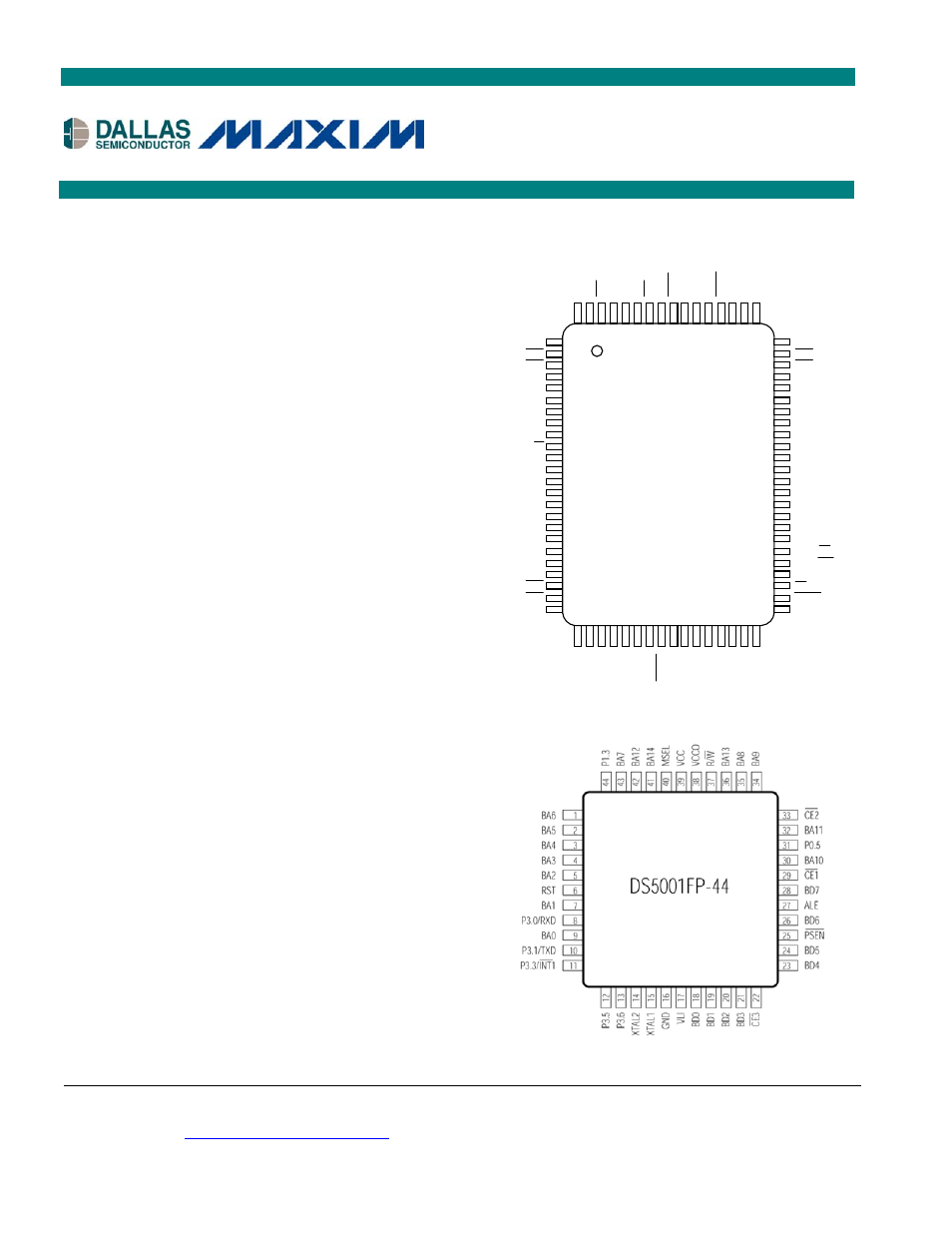

Features, Pin assignment (top view), Ds5001fp

1 of 26

052302

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple

revisions of any device may be simultaneously available through various sales channels. For information about device

errata, click here:

http://www.maxim-ic.com/errata

.

FEATURES

§ 8051-compatible microprocessor adapts to its

task

– Accesses up to 128kB of nonvolatile

SRAM

– In-system programming through on-chip

serial port

– Can modify its own program or data

memory

– Accesses memory on a separate byte-wide

bus

– Performs CRC-16 check of NV RAM

memory

– Decodes memory and peripheral chip

enables

§ High-reliability operation

– Maintains all nonvolatile resources for

over 10 years

– Power-fail reset

– Early warning power-fail interrupt

– Watchdog timer

– Lithium backs user SRAM for

program/data storage

– Precision bandgap reference for power

monitor

§ Fully 8051-compatible

– 128kB scratchpad RAM

– Two timer/counters

– On-chip serial port

– 32 parallel I/O port pins

§ Software security available with DS5002FP

secure microprocessor

PIN ASSIGNMENT (Top View)

P0.4AD4

CE2

PE2

BA9

P0.3/AD3

BA8

P0.2/AD2

BA13

P0.1/AD1

R/W

P0.0/AD0

VCC0

VCC

MSEL

P1.0

BA14

P1.1

BA12

P1.2

BA7

P1.3

PE3

PE4

BA6

P2.6/A14

CE3

CE4

BD3

P2.5/A13

BD2

P2.4/A12

BD1

P2.3/A11

BD0

VLI

BA15

GND

P2.2/A10

P2.1/A9

P2.0/A8

XTAL1

XTAL2

P3.7/RD

P3.6/WR

P3.5/TI

PF

VRST

P3.4/T0

DS5001FP

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

P1.4

BA5

P1.5

BA4

P1.6

BA3

P1.7

PROG

BA2

RST

BA1

P3.0/RXD

BA0

P3.1/TXD

P3.2/INT0

P3.3/INT1

BA11

P0.5/AD5

PE1

P0.6/AD6

BA10

P0.7/AD7

CE1

NC

CE1N

BD7

A

LE

BD6

PSEN

BD5

P2.7/A15

BD4

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

DS5001FP

128k Soft Microprocessor Chip

www.maxim-ic.com

80-Pin MQFP

44-Pin MQFP