9 port 0 direction regis, 10 port 1 direction regi, 9 port 0 direction register (pd0) -11 – Maxim Integrated MAXQ7667 User Manual

Page 86: 10 port 1 direction register (pd1) -11, Maxq7667 user’s guide, 9 port 0 direction register (pd0), 10 port 1 direction register (pd1)

5-11

__________________________________________________________________________________________________________

MAXQ7667 User’s Guide

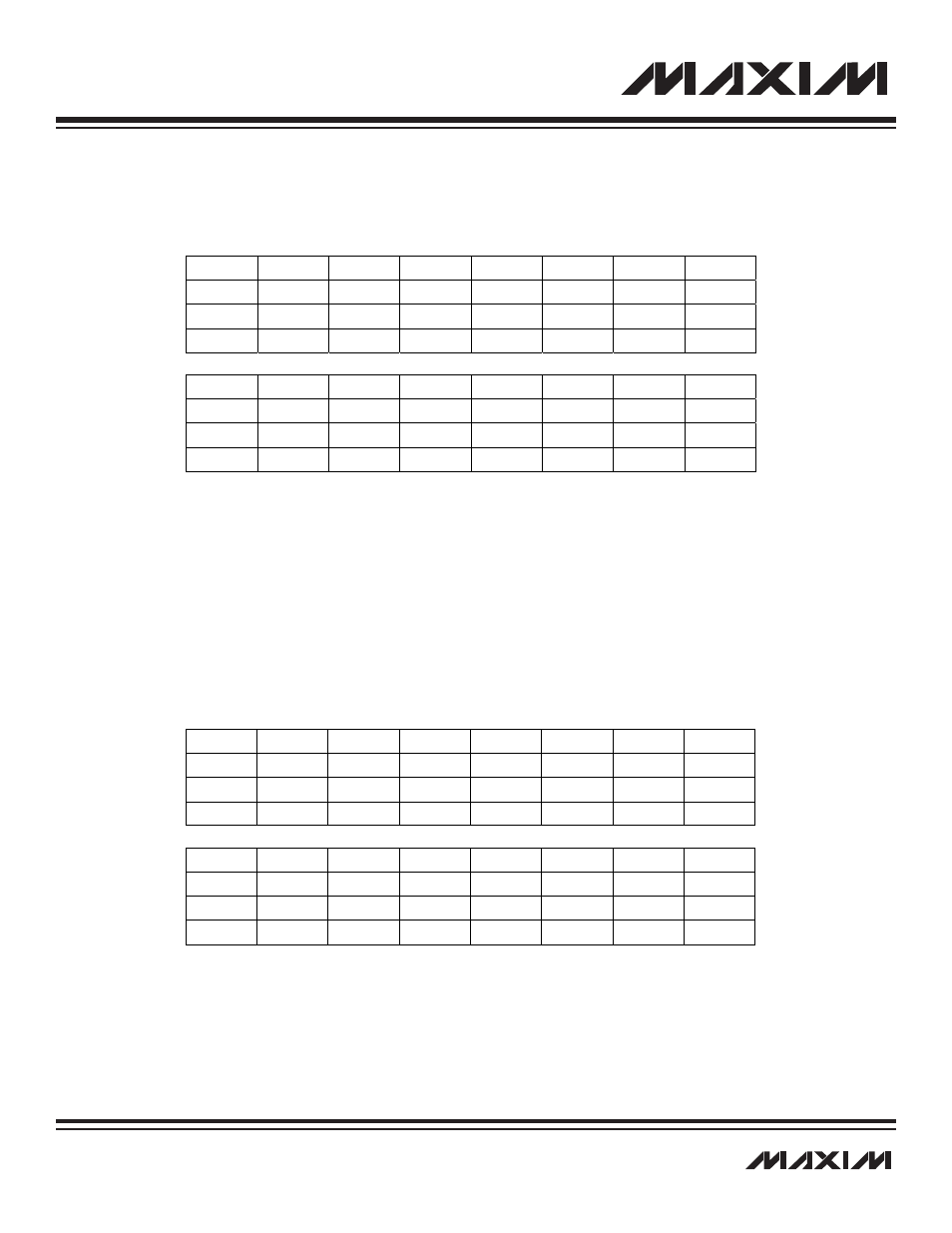

5.2.9 Port 0 Direction Register (PD0)

Register Description:

Port 0 Direction Register

Register Name:

PD0

Register Address:

Module 00h, Index 10h

Bits 15 to 8: Reserved. Read returns 0, write ignored.

Bits 7 to 0: Port 0 Direction Register Bits 7:0 (PD0[7:0]). Port 0 is an enhanced Type D I/O port. The PD0 register is used to determine

the direction of each pin that makes up the port. The port pins are independently controlled by their direction bit. When a bit in PD0 is set

to 1, its corresponding pin is enabled as an output. The data value in the respective bit of the PO register will be driven on the pin. When

a bit in PD0 is cleared to 0, its corresponding pin is available as an input, and allows an external signal to drive the pin. Note that each

port pin has weak pullup and pulldown resistors when functioning as an input, which is controlled by the respective PO bit. If the PO bit

is set to 1, this feature is enabled; if the PO bit is cleared to 0, this feature is disabled and the port pin is in high-impedance three-state.

5.2.10 Port 1 Direction Register (PD1)

Register Description:

Port 1 Direction Register

Register Name:

PD1

Register Address:

Module 00h, Index 11h

Bits 15 to 8: Reserved. Read returns 0, write ignored.

Bits 7 to 0: Port 1 Direction Register Bits 7:0 (PD1[7:0]). Port 1 is an enhanced Type D I/O port. PD1 is used to determine the direc-

tion of each pin that makes up the port. The port pins are independently controlled by their direction bit. When a bit in PD1 is set to 1,

its corresponding pin is used as an output. The data value in the respective bit of the PO register will be driven on the pin. When a bit

in PD1 is cleared to 0, its corresponding pin is available as an input, and allows an external signal to drive the pin. Note that each port

pin has weak pullup and pulldown resistors when functioning as an input, which is controlled by the respective PO bit. If the PO bit is

set to 1, this feature is enabled; if the PO bit is cleared to 0, this feature is disabled and the port pin is in high-impedance three-state.

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

PD07

PD06

PD05

PD04

PD03

PD02

PD01

PD00

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: This register is cleared to 00h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

PD17

PD16

PD15

PD14

PD13

PD12

PD11

PD10

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw