Maxim Integrated MAXQ7667 User Manual

Maxq7667 user’s guide, Maxq7667

______________________________________________________________________________________ Maxim Integrated Products

i

MAXQ7667 USER’S GUIDE

Rev 0; 4/09

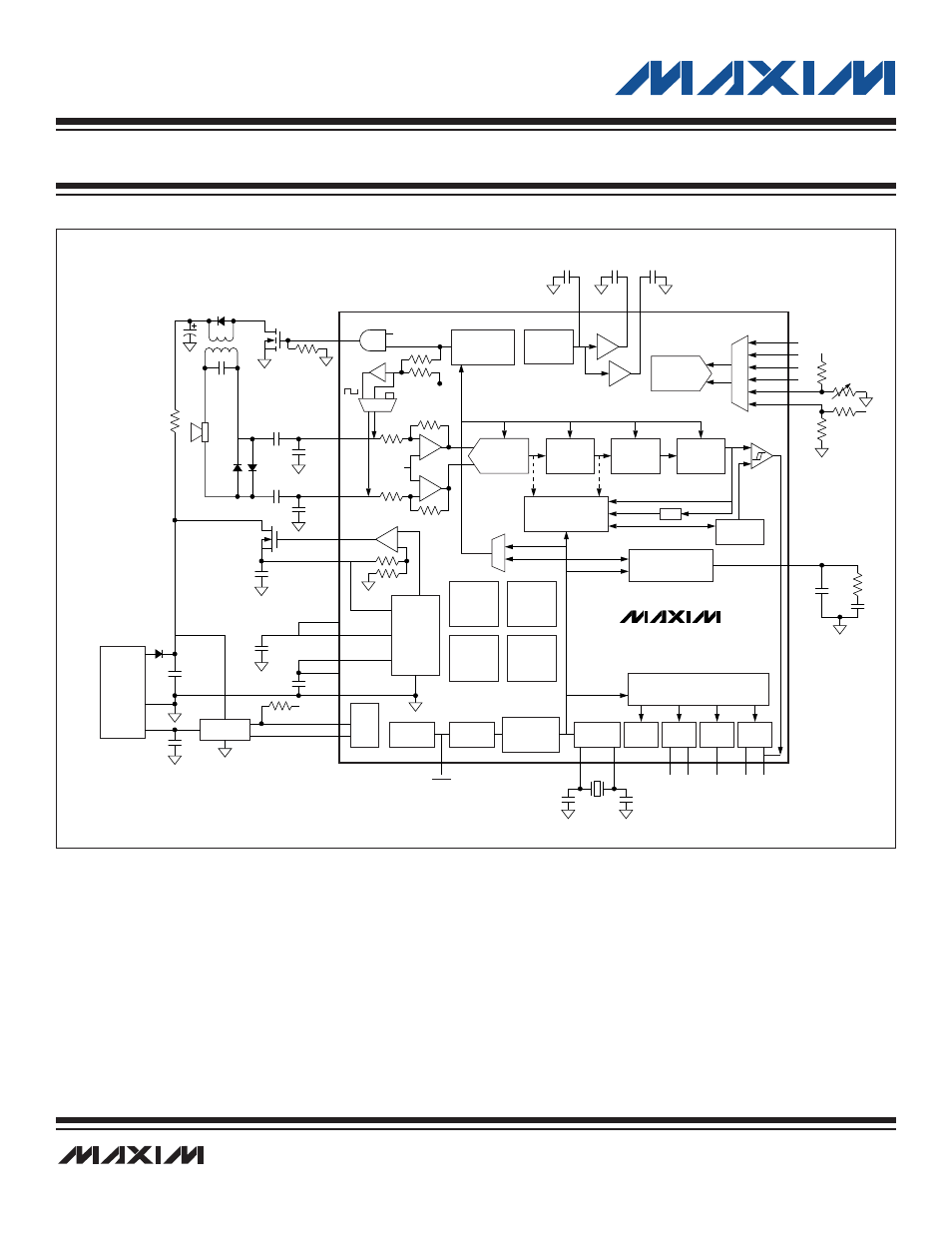

BURST ENABLE

AVDD/2

120k

Ω

LNA

AVDD/2

0mV

2mV

-1

MUX

BURST OUTPUT,

DUTY CYCLE, AND

PULSE COUNTER

SIGMA-DELTA

ADC

SIGMA-DELTA

ADC

DIGITAL

BANDPASS

FILTER

RAM

2K x 16

ROM

2K x 16

16 x 16

HW MULT

+ ACCUM

FLASH

8K x 16

OR

16K x 16

INTERNAL

REGULATORS

16-BIT 16-MIPS

MICROCONTROLLER

PROGRAMMABLE

PLL-BASED OSCILLATOR

VOLTAGE

REFERENCE

FULL WAVE

DETECTOR

THRESHOLD

ADJUST

SYSTEM

TIMER

TIMER 2

CRYSTAL

OSCILLATOR

16MHz (MAX)

INTERNAL

OSCILLATOR

WATCHDOG

POR/

BROWNOUT

UART

(LIN)

TIMER 1

TIMER 0

T0B_CMPO

T0

DIGITAL

LOWPASS

FILTER

120k

Ω

3k

Ω

3k

Ω

0.47

µF

REFBG

0.47

µF

0.47

µF

REFSAR

REFECHO

AIN0

BURST

ECHON

470pF

0.01

µF

ECHOP

GATE5

AVDD

DVDD

GND

Rx

Tx

DVDDIO

REG3P3

REG2P5

+5.0V DVDDIO

BSP129

AVDD

330pF

THERMISTOR

BATTERY+

AIN1

AIN2

AIN3

AIN4

AIN5

FILT

T1

T2

16MHz

20pF

20pF

T2B

RESET

CLOCK PRESCALERS

DIVIDE BY 1 TO 128

FIFO

33nF

24k

Ω

470pF

0.01

µF

0.1

µF

0.1

µF

0.1

µF

TRANSCEIVER

CONNECTOR

V+

GROUND

SIGNAL

+9V TO

+20V

MAXQ7667

Document Outline

- TABLE OF CONTENTS

- SECTION 1: OVERVIEW

- SECTION 2: ARCHITECTURE

- SECTION 3: PROGRAMMING

- SECTION 4: REGISTER DESCRIPTIONS

- 4.1 System Register Descript...

- 4.1.1 Accumulator Pointer Re...

- 4.1.2 Accumulator Pointer Co...

- 4.1.3 Processor Status Flags...

- 4.1.4 Interrupt and Control ...

- 4.1.5 Interrupt Mask Registe...

- 4.1.6 System Control Registe...

- 4.1.7 Interrupt Identificati...

- 4.1.8 System Clock Control R...

- 4.1.9 Watchdog Timer Control...

- 4.1.10 Accumulator n Registe...

- 4.1.11 Prefix Register (PFX[n])

- 4.1.12 Instruction Pointer R...

- 4.1.13 Stack Pointer Registe...

- 4.1.14 Interrupt Vector Regi...

- 4.1.15 Loop Counter 0 Regist...

- 4.1.16 Loop Counter 1 Regist...

- 4.1.17 Frame Pointer Offset ...

- 4.1.18 Data Pointer Control ...

- 4.1.19 General Register (GR)

- 4.1.20 General Register Low ...

- 4.1.21 Frame Pointer Base Re...

- 4.1.22 General Register Byte...

- 4.1.23 General Register High...

- 4.1.24 General Register Sign...

- 4.1.25 Frame Pointer Registe...

- 4.1.26 Data Pointer 0 Regist...

- 4.1.27 Data Pointer 1 Regist...

- 4.2 Peripheral Register Modules

- 4.1 System Register Descript...

- SECTION 5: GENERAL-PURPOSE I/O MODULE

- 5.1 Architecture

- 5.2 Port Registers

- 5.2.1 Port 0 Output Register...

- 5.2.2 Port 1 Output Register...

- 5.2.3 External Interrupt Fla...

- 5.2.4 External Interrupt Fla...

- 5.2.5 Port 0 Input Register ...

- 5.2.6 Port 1 Input Register ...

- 5.2.7 External Interrupt Ena...

- 5.2.8 External Interrupt Ena...

- 5.2.9 Port 0 Direction Regis...

- 5.2.10 Port 1 Direction Regi...

- 5.2.11 External Interrupt Ed...

- 5.2.12 External Interrupt Ed...

- 5.2.13 Pad Drive Strength Re...

- 5.2.14 Pad Drive Strength Re...

- 5.2.15 Pad Resistive Pull Di...

- 5.2.16 Pad Resistive Pull Di...

- 5.3 GPIO Operation

- SECTION 6: TYPE 2 TIMER/COUNTER MODULE

- 6.1 Architecture

- 6.2 Type 2 Timer/Counter Per...

- 6.3 Type 2 Status/Control Re...

- 6.4 Type 2 Counter Registers

- 6.5 Type 2 Reload Register

- 6.6 Type 2 Capture/Compare R...

- 6.7 Type 2 Timer/Counter Ope...

- SECTION 7: SCHEDULE TIMER

- SECTION 8: UART AND LIN

- 8.1 Architecture

- 8.2 UART/LIN Pins

- 8.3 UART and LIN Register De...

- 8.3.1 Control Register 1 (UA...

- 8.3.2 Serial Control Registe...

- 8.3.3 Serial Port Buffer Reg...

- 8.3.4 FIFO Status Register (...

- 8.3.5 Error Register (UART) ...

- 8.3.6 Checksum Register (UAR...

- 8.3.7 Interrupt State Vector...

- 8.3.8 Status Register 0 (UAR...

- 8.3.9 Serial Mode Register (...

- 8.3.10 FIFO Control Register...

- 8.3.11 Control Register 0 (U...

- 8.3.12 Control Register 2 (U...

- 8.3.13 Identifier Boundary R...

- 8.3.14 Serial Address Regist...

- 8.3.15 Serial Address Mask R...

- 8.3.16 Bit Timing Register (...

- 8.3.17 Timer Register (UART)...

- 8.4 MAXQ7667 LIN

- 8.5 MAXQ7667 UART

- SECTION 9: ENHANCED SERIAL PERIPHERAL INTERFACE (SPI) MODULE

- SECTION 10: HARDWARE MULTIPLIER MODE

- SECTION 11: TEST ACCESS PORT (TAP)

- SECTION 12: IN-CIRCUIT DEBUG MODE

- 12.1 Architecture

- 12.2 In-Circuit Debug Periph...

- 12.3 Debug Engine Operation

- SECTION 13: IN-SYSTEM PROGRAMMING/BOOTLOADER

- SECTION 14: SAR ADC MODULE

- SECTION 15: OSCILLATOR/CLOCK GENERATION

- SECTION 16: POWER-SUPPLY/SUPERVISORY MONITORING

- SECTION 17: ULTRASONIC DISTANCE MEASUREMENT MODULE--BURST TRANSMISSION AND ECHO RECEPTION

- 17.1 Architecture

- 17.2 Burst Transmission and ...

- 17.3 Echo Burst Transmission...

- 17.3.1 Burst Pulse-Width Hig...

- 17.3.2 Burst Transmit Contro...

- 17.3.3 Echo Path Control Reg...

- 17.3.4 PLL-Based Programmabl...

- 17.3.5 Analog Interrupt Enab...

- 17.3.6 Echo Envelope Compara...

- 17.3.7 Echo Envelope Compara...

- 17.3.8 Analog Status Registe...

- 17.3.9 Echo Envelope Lowpass...

- 17.3.10 Echo Envelope Bandpa...

- 17.3.11 Echo Envelope Bandpa...

- 17.3.12 Echo Envelope Lowpas...

- 17.3.13 Echo Envelope Lowpas...

- 17.3.14 Analog Power Enable ...

- 17.4 Burst Signal Generation

- 17.5 Echo Reception

- SECTION 18: UTILITY ROM

- SECTION 19: INSTRUCTION SET SUMMARY

- ADD/ADDC src

- AND src

- AND Acc.

- {L/S}CALL

- CMP src

- CPL

- CPL C

- {L/S}DJNZ LC[n], src

- {L/S}JUMP src

- {L/S}JUMP C/{L/S}JUMP NC, sr...

- MOVE dst, src

- MOVE Acc., C

- MOVE C, Acc.

- MOVE C, src.

- MOVE C, #0

- MOVE C, #1

- MOVE dst., #0

- MOVE dst., #1

- NEG

- OR src

- OR Acc.

- POP dst

- POPI dst

- PUSH src

- RET

- RET C/RET NC, RET Z/RET NZ, ...

- RETI

- RETI C/RETI NC, RETI Z/RETI ...

- RL/RLC

- RR/RRC

- SLA/SLA2/SLA4

- SR/SRA/SRA2/SRA4

- SUB/SUBB src

- XCH

- XCHN

- XOR src

- XOR Acc.

- REVISION HISTORY