Figure 17-5. comparator hysteresis -23, Table 17-8. fifo load source selection -23, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 305: Table 17-8. fifo load source selection

The amplified echo signal passes through a BPF, a full-wave rectifier, and an LPF.

After the echo signal goes through these filtering and signal processing stages, the LPF data is available from the LPFD register. This

data is automatically updated at a rate equal to 5 x B

FREQ

. LPFD can be read directly by the processor or it can be loaded into an 8-

words deep FIFO. If the FIFO is used, the source that initiates a FIFO load is selected by setting the FIFO load source bits, FFLS.[2:0]

(LPFC[2:0]) as shown in Table 17-8.

Table 17-8. FIFO Load Source Selection

The output of the LPF (LPFD register) is automatically sent to a digital comparator where the LPFD register is compared to the Echo

Envelope Comparator Threshold register (CMPT[15:0]). This happens even if LPFD is not read or loaded into the FIFO.

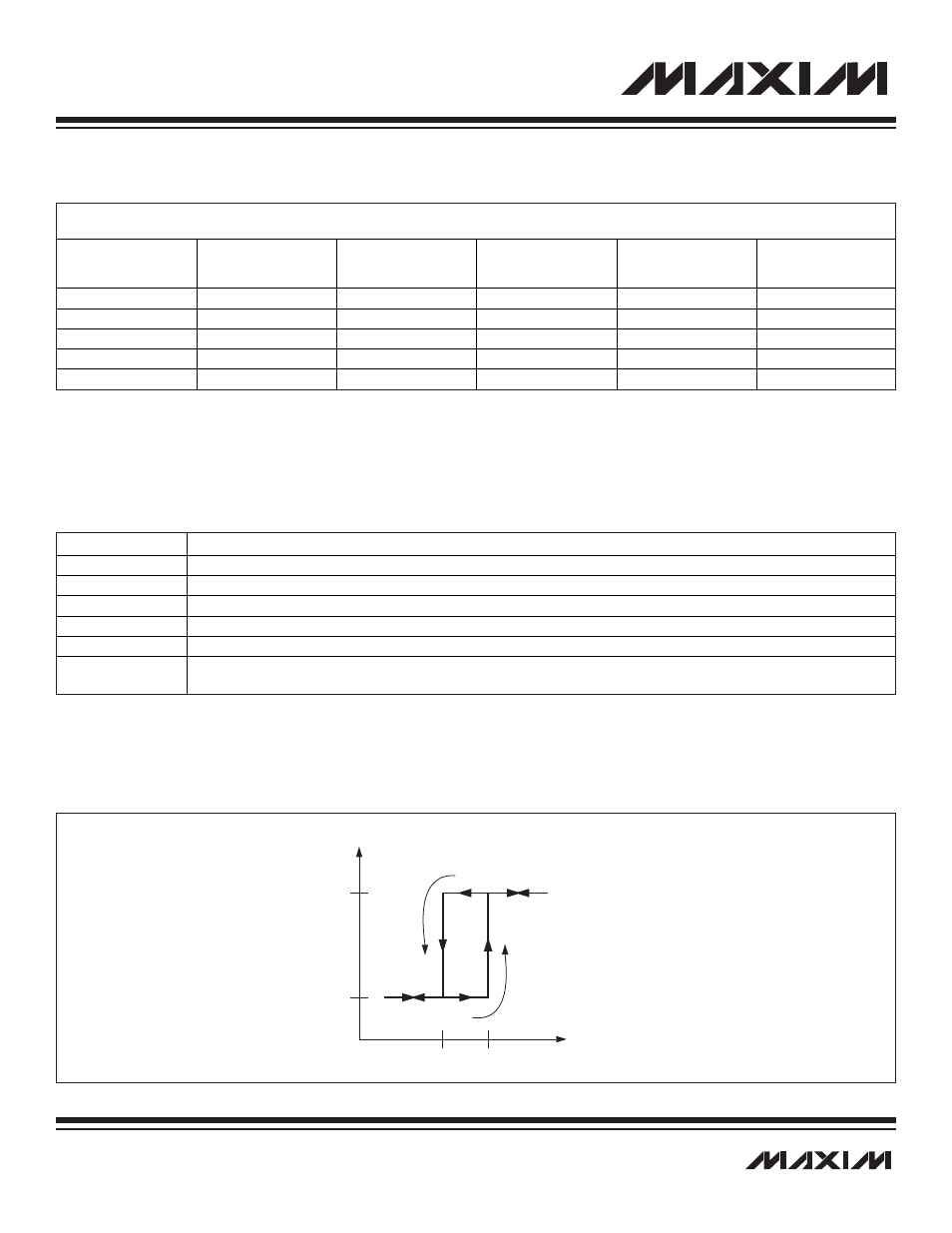

The output of the comparator, CMPLVL, depends on the values of the following: CMPT register, LPFD register, CMPH[14:0] bits

(CMPC.14:0) (comparator hysteresis), and CMPP bit (comparator polarity) (CMPC.15). CMPP selects the edge of the CMPLVL that

causes a comparator interrupt. Figure 17-5 represents the link between the registers and CMPLVL output.

17-23

_________________________________________________________________________________________________________

MAXQ7667 User’s Guide

ECHO RECEIVE PATH GAIN FROM THE ECHO INPUTS TO THE LOWPASS FILTER OUTPUT

(GAIN IS CONTROLLED BY THE VALUE IN RCVGN BIT)

RCVGN

FULL SCALE

(mV

P-P

)

LPFD

RESOLUTION

(µV

P-P

/LSB)

RCVGN

FULL SCALE

(mV

P-P

)

LPFD RESOLUTION

(µV

P-P

/LSB)

0b01011

37.35

0.57

0b11011

9.17

0.14

0b01100

34.08

0.52

0b11100

8.52

0.13

0b01101

31.46

0.48

0b11101

7.86

0.12

0b01110

29.49

0.45

0b11110

7.21

0.11

0b01111

27.52

0.42

0b11111

6.55

0.10

FFLS[2:0]

FIFO LOAD SOURCE

000

Timer 0

001

Timer 1

010

Timer 2

011, 100, 101

Reserved

110

Continuous loading whenever data is ready at the LPF indicated by the LPFRDY bit.

111

Software loaded. Selects the FIFO load control bit, FFLD (LPFC.3). When software sets FFLD = 1, the output of the lowpass filter

(LPFD register) is put into the FIFO. FFLD = 0 has no effect. FFLD is automatically reset to 0 after the FIFO is loaded.

Table 17-7. Effective Gain for the Echo Reception Stage (continued)

1

0

CMPT-CMPH

CMPT

LPFD

CMPLVL

CMPP = 1 SETS UP THE

INTERRUPT TO TRIGGER

ON A FALLING EDGE

CMPP = 0 SETS UP THE

INTERRUPT TO TRIGGER

ON A RISING EDGE

Figure 17-5. Comparator Hysteresis