5 analog interrupt enab, 5 analog interrupt enable register (aie) -10, Maxq7667 user’s guide – Maxim Integrated MAXQ7667 User Manual

Page 292: 5 analog interrupt enable register (aie)

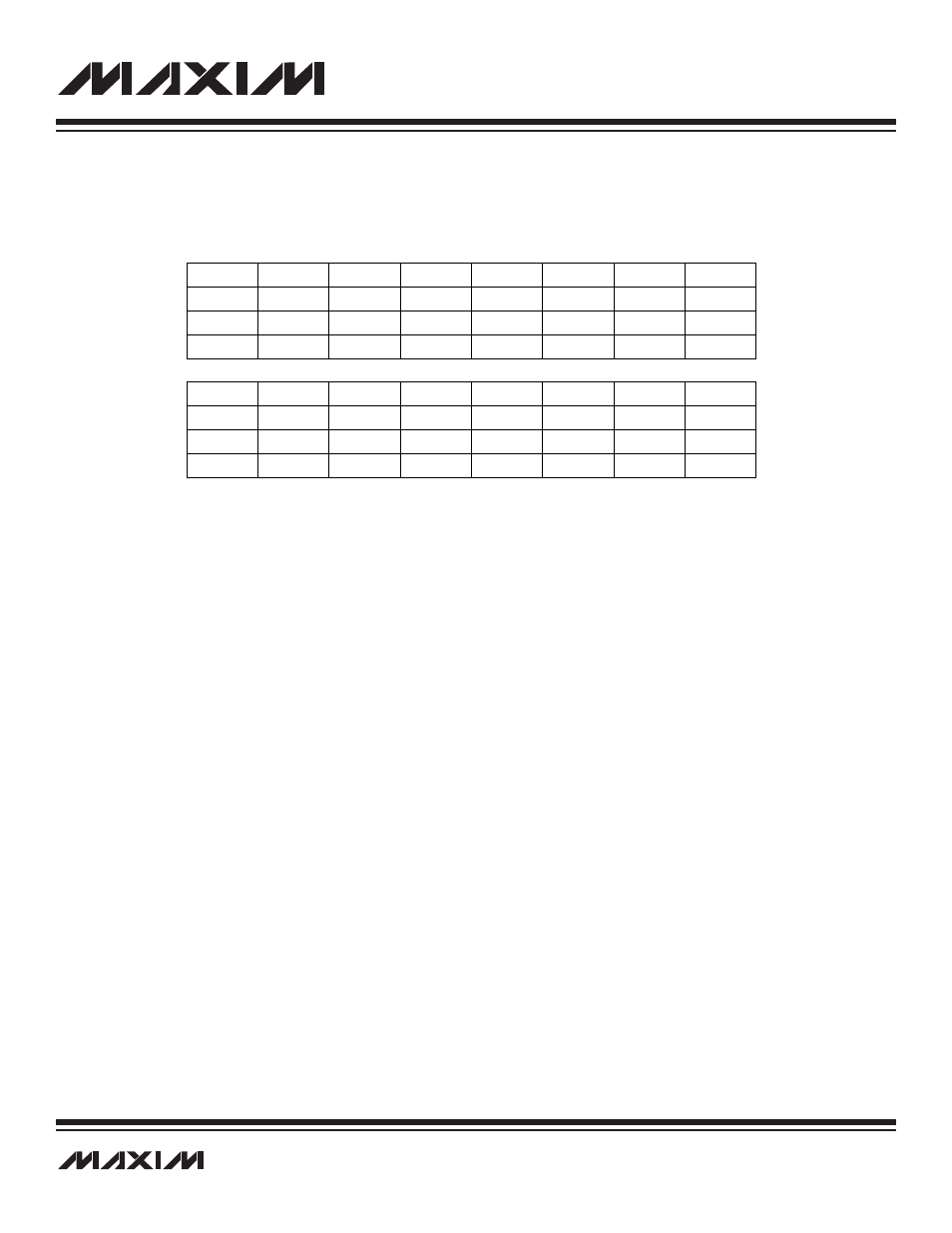

17.3.5 Analog Interrupt Enable Register (AIE)

Register Description:

Analog Interrupt Enable Register

Register Name:

AIE

Register Address:

Module 05h, Index 05h

Bits 15 to 8: Reserved. Read returns 0.

Bit 7: Crystal Oscillator Failure (XTIE). See Section 15 for details on this bit.

Bit 6: DVDDIO Brownout Interrupt Enable (VIBIE). See Section 16 for details on this bit.

Bit 5: DVDD Brownout Interrupt Enable (VDBIE). See Section 16 for details on this bit.

Bit 4: AVDD Brownout Interrupt Enable (VABIE). See Section 16 for details on this bit.

Bit 3: Echo Envelope Comparator Interrupt Enable (CMPIE). When set to 1, this bit allows an interrupt request to be generated when

the echo envelope comparator crosses the threshold. See Figure 17-5 and the description of the CMPP bit (CMPC.15) for further

details. The interrupt, when enabled, is triggered by changes in the CMPLVL signal (ASR.12).

Bit 2: Echo Envelope Lowpass Filter FIFO Full Interrupt Enable (LFLIE). When set to 1, this bit allows an interrupt request to be

generated when the echo receive path FIFO is full or has overflowed. The interrupt, when enabled, is triggered by the FIFO full flag,

LPFFL (ASR.2), and an internal overflow flag.

Bit 1: Echo Envelope Lowpass Filter Output Data Ready Interrupt Enable (LPFIE). When set to 1, this bit allows an interrupt request

to be generated when the echo receive path LPFD register receives a new value. The interrupt, when enabled, is triggered by changes

in the LPFRDY signal (ASR.1).

Bit 0: SAR ADC Data Ready Interrupt Enable (SARIE). See Section 14 for details on this bit.

_________________________________________________________________________________________________________

17-10

MAXQ7667 User’s Guide

r = read, w = write

Note: AIE is cleared to 0000h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

—

—

—

—

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

XTIE

VIBIE

VDBIE

VABIE

CMPIE

LFLIE

LPFIE

SARIE

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw