13 identifier boundary r, 14 serial address regist, 13 identifier boundary register (uart) (idfb) -15 – Maxim Integrated MAXQ7667 User Manual

Page 145: 14 serial address register (uart) (saddr) -15, Maxq7667 user’s guide, 13 identifier boundary register (uart) (idfb), 14 serial address register (uart) (saddr)

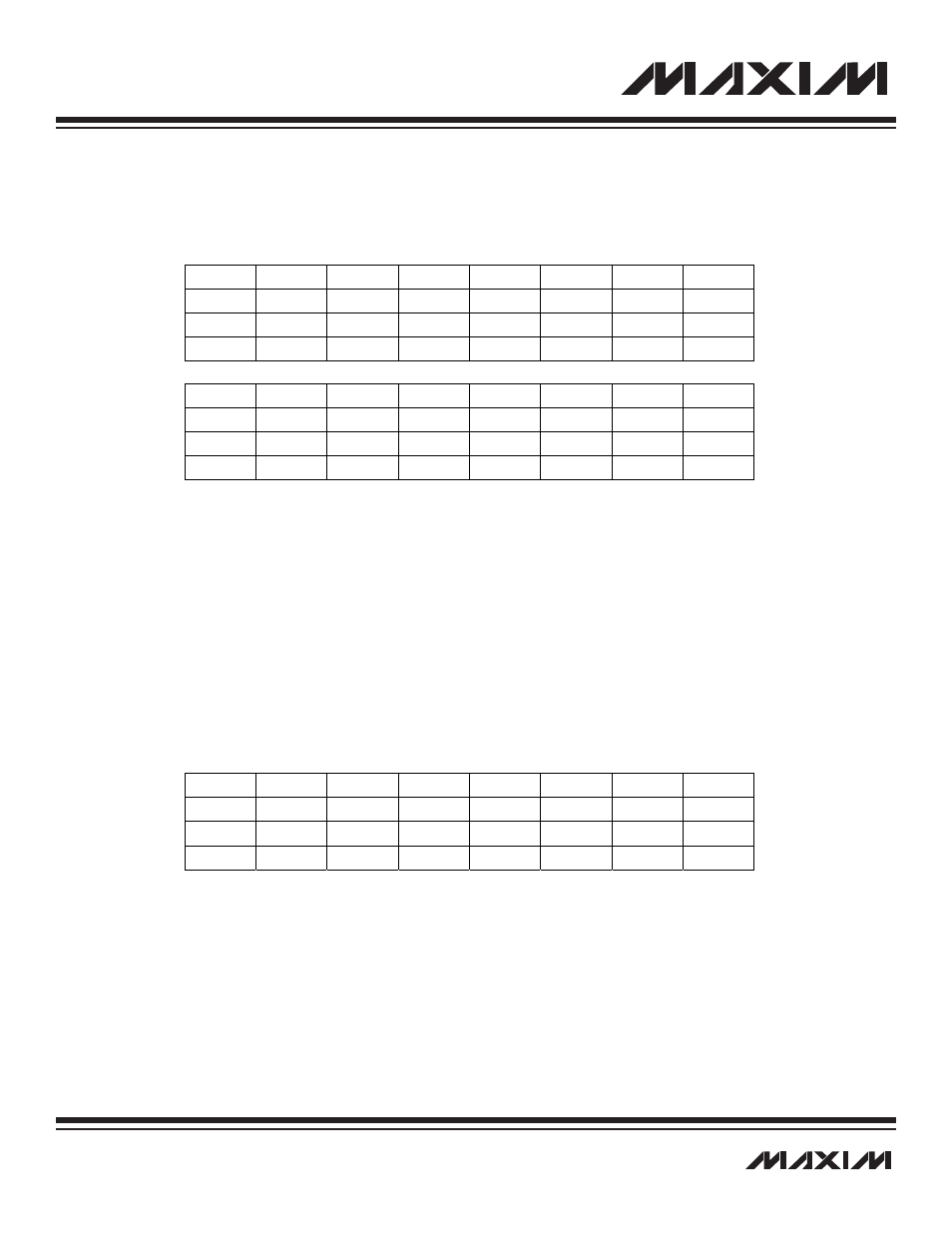

8.3.13 Identifier Boundary Register (UART) (IDFB)

Register Description:

Identifier Boundary Register

Register Name:

IDFB

Register Address:

Module 03h, Index 16h

Bits 15, 14, 7, and 6: Reserved. Read returns 0.

Bits 13 to 8: Identifier Boundary High 13:8 (IDFBH[5:0]). This field selects the upper limit for a valid identifier. If the peripheral

receives a header with an identifier that is higher than this limit, the remainder of the frame is ignored. Note that frames with an identi-

fier in the inclusive range 38h–3Fh are always considered valid (the 3Ch–3Fh range is used by LIN 2.0 control frames and the 38h–3Bh

range is used by SAE J2602 control frames).

Bits 5 to 0: Identifier Boundary Low 5:0 (IDFBL[5:0]). This field selects the lower limit for a valid identifier. If the peripheral receives

a header with an identifier below this limit, the remainder of the frame is ignored.

8.3.14 Serial Address Register (UART) (SADDR)

Register Description:

Serial Address Register

Register Name:

SADDR

Register Address:

Module 03h, Index 17h

Bits 7 to 0: Serial Address Register 7:0 (SADDR[7:0]). In legacy UART mode, this register can be written by the host to configure

the address of the peripheral in one of the 9-bit communication modes (mode 2 or mode 3). This register serves no function if the

peripheral is configured for LIN master or LIN slave mode.

8-15

__________________________________________________________________________________________________________

MAXQ7667 User’s Guide

r = read, w = write

Note: IDFB is cleared to 3F00h on all forms of reset.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

IDFBH5

IDFBH4

IDFBH3

IDFBH2

IDFBH1

IDFBH0

Reset

0

0

1

1

1

1

1

1

Access

r

r

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

—

—

IDFBL5

IDFBL4

IDFBL3

IDFBL2

IDFBL1

IDFBL0

Reset

0

0

0

0

0

0

0

0

Access

r

r

rw

rw

rw

rw

rw

rw

r = read, w = write

Note: SADDR is cleared to 00h on all forms of reset.

Bit #

7

6

5

4

3

2

1

0

Name

SADDR7

SADDR6

SADDR5

SADDR4

SADDR3

SADDR2

SADDR1

SADDR0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw