4 external oscillator clo, 5 watchdog timer, 5 watchdog timer -12 – Maxim Integrated MAXQ7667 User Manual

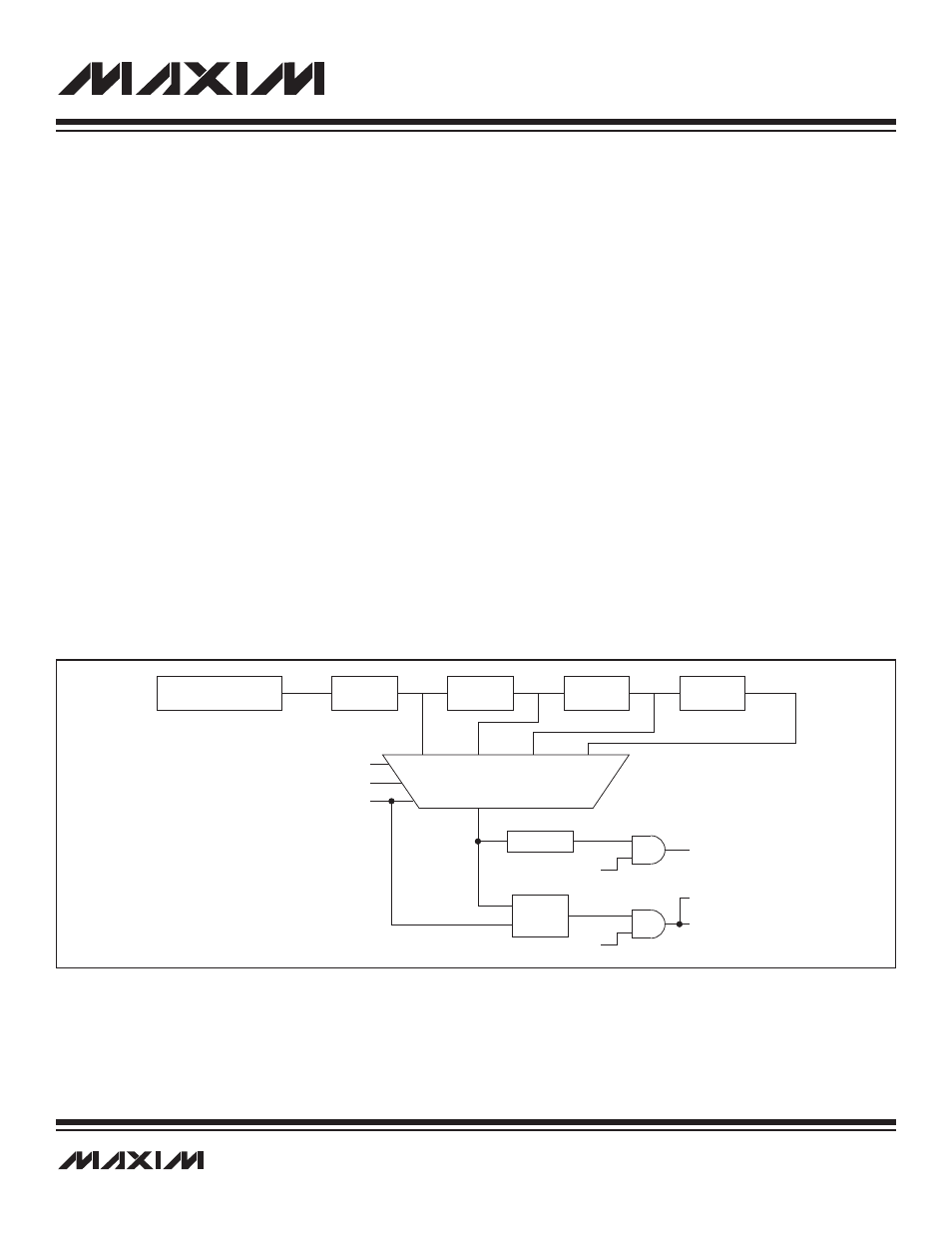

Page 264: Figure 15-2. watchdog timer function -12, Maxq7667 user’s guide

15.4 External Oscillator Clock/Crystal Failure Switchover

The external oscillator clock/crystal failure can occur during normal operation and is detected when the XTRDY bit switches over to 0,

indicating that the external source has failed. The hardware forces a switch to the internal RC oscillator to keep the MAXQ7667 proces-

sor operational.

The following must be true to detect the failure on the high-frequency input:

•

XTRC must be set to logic 1, which enables the external clock source and selects external clock/crystal as the active clock

source.

•

XTRDY bit is set to 1, which indicates external clock is ready.

•

A falling edge is detected on the XTRDY bit, which signals a crystal/clock source failure.

When the above conditions have been detected, the clock circuitry will:

•

Enable the RC oscillator immediately, regardless of the original state of the RCE bit.

•

Switch the clock source from external to internal by forcing XTRC to 0.

•

Make the system clock ready after a few clock cycles delay.

•

Set the high-frequency crystal failure interrupt XTI (AIE.7) flag to 1; an interrupt is generated if the interrupt was enabled, XTIE

= 1 (ASR.7).

This switchover remains until software reconfigures the clock structure.

15.5 Watchdog Timer

Generally, the primary function of the watchdog timer is to provide system control in case a software problem occurs; the watchdog

timer performs a controlled system restart when the selected time interval expires.

The watchdog timer is driven by the internal RC clock, as illustrated in Figure 15-2. If the watchdog is enabled, the RC clock remains

turned on, even after the system clock has been switched over to the external source (XTRC = 1).

_________________________________________________________________________________________________________

15-12

MAXQ7667 User’s Guide

16MHz INTERNAL RC CLOCK

(MAXIMUM SETTING)

DIVIDE

BY 2

12

256ms

2048ms

16,384ms

131,072ms

DIVIDE

BY 2

3

DIVIDE

BY 2

3

WDCN.3:WDIF

RESET

DELAY

DIVIDE

BY 2

3

TIMER

WD1

TIMEOUT

WATCHDOG

INTERRUPT

WATCHDOG

RESET

WDCN.2:WTRF

WDCN.6:EWDI

WDCN.1:EWT

WD0

RWT

Figure 15-2. Watchdog Timer Function